#### Programmable Logic Controllers and Microcontrollers (5<sup>th</sup> Sem)

Electrical Engineering Department, Govt. Polytechnic Panchkula

#### Table of Contents

- 1. Chapter-1: Introduction to PLC

- 2. Chapter-2: Working of PLC

- 3. Chapter-3: Ladder Diagram Programming

- Chapter-4: Applications of PLCs 4.

- 5. Chapter-5: Introduction to SCADA

- 6. Chapter-6: Micro Controller Series (MCS)-51 Over View

- 7. Chapter-7: Instruction Set and Addressing Modes of 8051

- 8. Chapter-8 : Assembly language programming

- 9. Chapter-9: Design and Interfacing with 8051

- 10. Chapter-10 : Application of Micro controllers

# CHAPTER – 1 Introduction to PLC

#### Concept of PLC

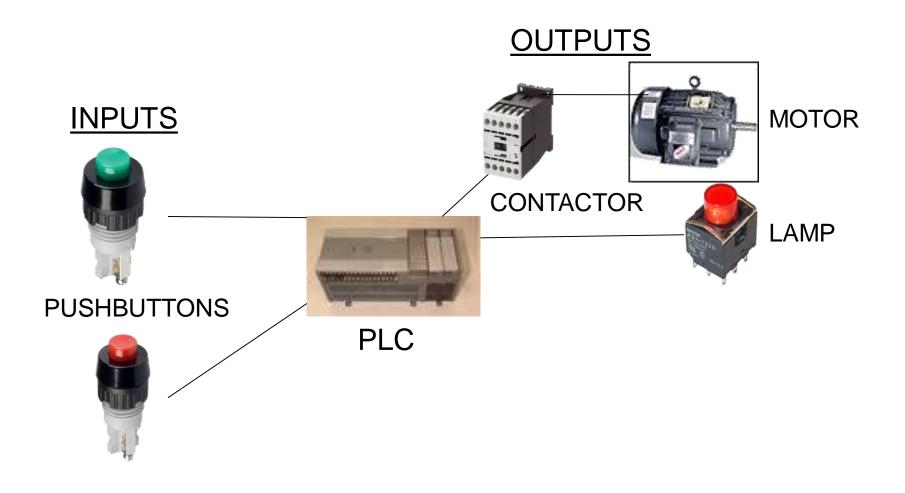

A PROGRAMMABLE LOGIC CONTROLLER (PLC) is an industrial computer control system that continuously monitors the state of input devices and makes decisions based upon a custom program to control the state of output devices.

Their primary goal of PLC is

To eliminate the high costs associated with inflexible, relay-controlled systems

# **Basic PLC Elements**

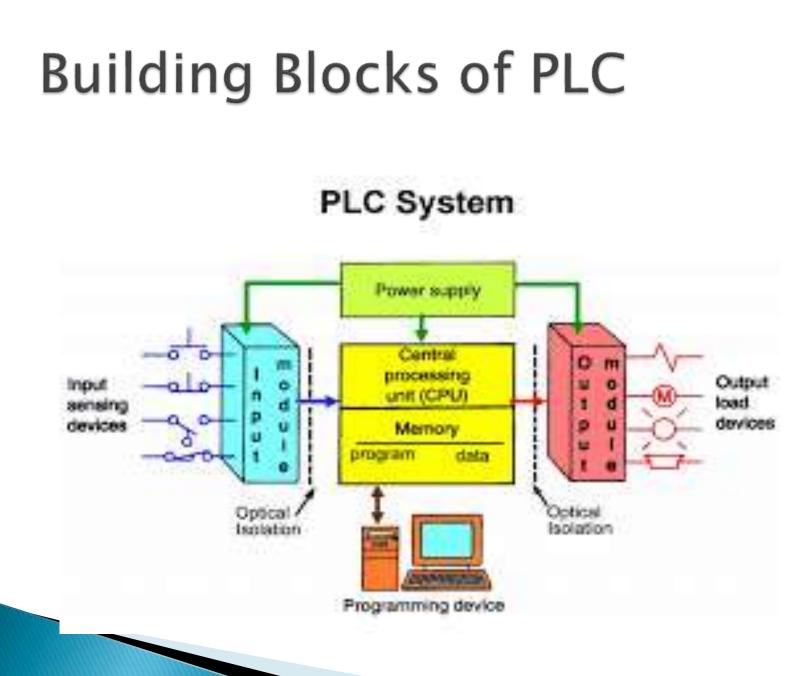

- The basic elements of a PLC include input modules or points, a Central Processing Unit (CPU), output modules or points, and a programming device.

- The type of input modules or points used by a PLC depend upon the types of input devices used. Some input modules or points respond to digital inputs, also called discrete inputs, which are either on or off. Other modules or inputs respond to analog signals.

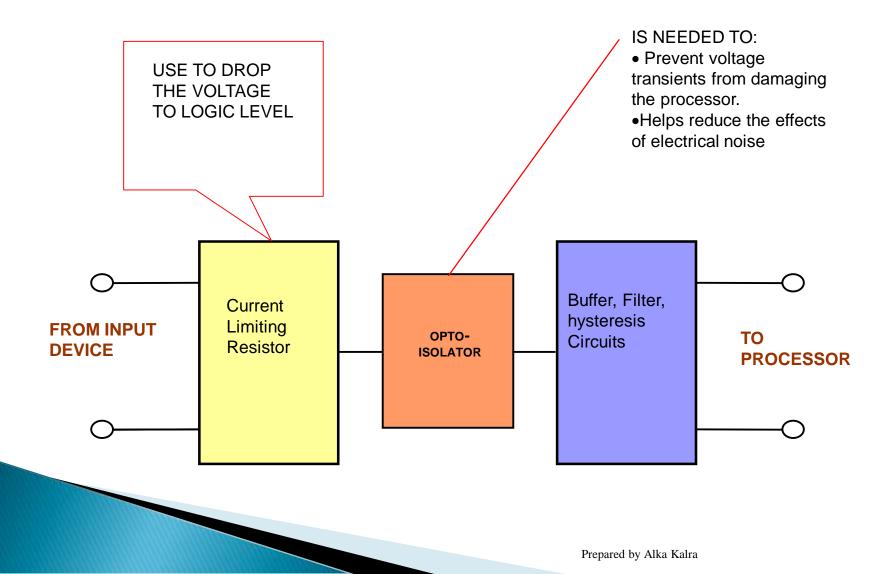

# PLC Input Circuit

- The primary function of a PLC's input circuitry is to convert the signals provided by these various switches and sensors into logic signals that can be used by the CPU.

- The CPU evaluates the status of inputs, outputs, and other variables as it executes a stored program.

- The CPU then sends signals to update the status of outputs.

# **Programming Device**

- The programming device is used to enter or change the PLC's program or to monitor or change stored values.

- Once entered, the program and associated variables are stored in the CPU.

- In addition to these basic elements, a PLC system may also incorporate an operator interface device of some sort to simplify monitoring of the machine or process.

#### Difference between relay and PLC

- The difference between a PLC and relay logic is that a PLC is a programmable device where as relay logic is a network of hardwired electrical devices.

- Both a PLC and relay logic can perform logical computation, but a PLC does it using a microprocessor and relay logic does it using electric circuits

# Limitations of Relays

- Prior to PLCs, many control tasks were performed by contactors, control relays and other electromechanical devices. This is often referred to as hard-wired control.

- Circuit diagrams had to be designed, electrical components specified and installed, and wiring lists created. If an error was made, the wires had to be reconnected correctly. A change in function or system expansion required extensive component changes and rewiring.

- Requires periodic maintenance and testing.

- Relay operation can be affected due to ageing of the components and dust, pollution resulting in spurious trips

- Operation speed for an electromagnetic relays is limited by the mechanical inertia of the component

#### Advantages of PLC over Electromagnetic Relays

- Smaller physical size than hard-wire solutions.

- Easier and faster to make changes.

- PLCs have integrated diagnostics and override functions.

- Diagnostics are centrally available.

- Applications can be immediately documented.

- Applications can be duplicated faster and less expensively.

#### PLC Size

#### • <u>1. SMALL</u>

- it covers units with up to 128 I/O's and memories up to 2 Kbytes.

- ▶ <u>2. MEDIUM</u>

- They have up to 2048 I/O's and memories up to 32 Kbytes.

- 3. LARGE

- They have up to 8192 I/O's and memories up to 750 Kbytes.

# PLC Programming Languages

There are only 5 languages that are considered to be standard languages for use on PLCs, according to IEC section 61131-3.

- Ladder Diagram (LD)

- A sequential function chart

- Function Block Diagram

- Instruction List

- Structured Text

# Ladder Diagram

- Ladder Diagram is the oldest PLC language. This graphical programming language was modeled from relay logic to allow engineers and electricians to transition smoothly into programming PLCs.

- Within Ladder, rungs and rails represent the real world electrical connections. Specifically, the vertical "rails" represent the supply power of the device while the rungs that are connected to the rails are equal to the amount of control circuits.

#### **Sequential Function Charts**

- A sequential function chart is a graphical programming language that mimics a flow chart. You use steps and transitions to get output.

- Steps are functions within the program and house events that are activated based on state and other specified conditions.

- Transitions are instructions based on true/false values that move you from one step to another.

- Branches are used to initiate multiple steps at a time. The branches act like threads where functions can run concurrently.

- All of these steps, transitions, and branches are housed in a series of scripts that execute in a procedural manner. The visual nature of the language allows users to monitor processes that both heavily use conditional logic and run parallel instructions. PLCs that are prone to suffering from bottlenecks can be more intuitively maintained and troubleshooted using the chart to follow the logic of the program.

#### Function Block Diagram

- Block based programming languages are a type of graphical language that minimizes code into blocks, which allows for a simple way to create executable commands.

- FBD in particular describes a function between inputs and outputs that are connected by connection lines. The logic of the inputs and outputs are stored in blocks. The blocks are programmed onto sheets and the PLC scans these sheets in order or by specified connections between blocks, much like procedural languages.

- The I/O focus mirrors that of ladder logic. Yet, the code that the blocks contain allow engineers to develop more complex batch control tasks among other repeatable tasks.

#### Instruction List

- This is the PLC's equivalent to assembly language. This gives you immediate access to the machine itself, which allows you to write code that is compressed and fast. The code is represented in the manner that the language's name suggests: in a list of commands.

- Structured Text is a high level language designed to program PLCs. This is essentially the C++ of the PLC world. Any PLC that requires complex data handling will most likely use ST.

#### Structured Text

Structured Text is a high level language designed to program PLCs. This is essentially the C++ of the PLC world. Any PLC that requires complex data handling will most likely use ST.

#### Advantages of PLCs

- Less wiring.

- Wiring between devices and relay contacts are done in the PLC program.

- Easier and faster to make changes.

- Trouble shooting aids make programming easier and reduce downtime.

- Reliable components make these likely to operate for years before failure.

# PLC Manufacturer/Brands

| AMERICAN | 2.<br>3.<br>4.<br>5.<br>6.                                             | Allen Bradley<br>Gould Modicon<br>Texas Instruments<br>General Electric<br>Westinghouse<br>Cutter Hammer<br>Square D |

|----------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| EUROPEAN | <ol> <li>2.</li> <li>3.</li> <li>4.</li> <li>1.</li> <li>2.</li> </ol> | Siemens<br>Klockner & Mouller<br>Festo<br>Telemechanique<br>Toshiba<br>Omron<br>Fanuc                                |

4. Mitsubishi

# Applications of PLC

- Manufacturing / Machining

- Food / Beverage

- Metals

- Power

- Mining

- Petrochemical / Chemical

# CHAPTER-2

# Working of PLC

Prepared by Mrs. Alka Kalra

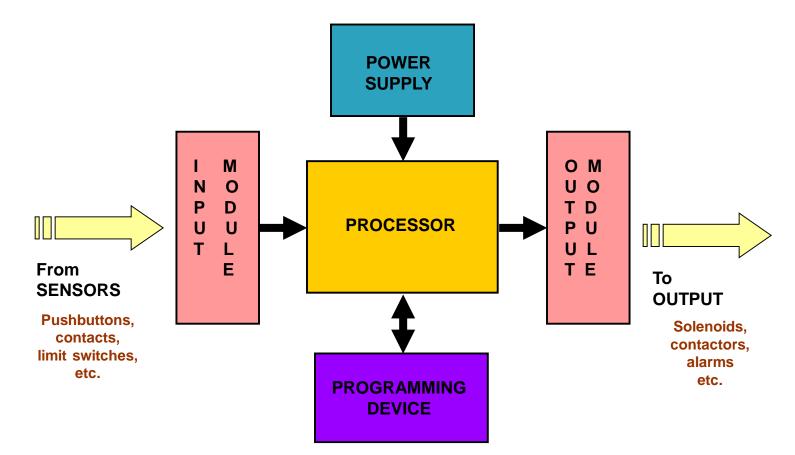

#### Major Components of a Common PLC

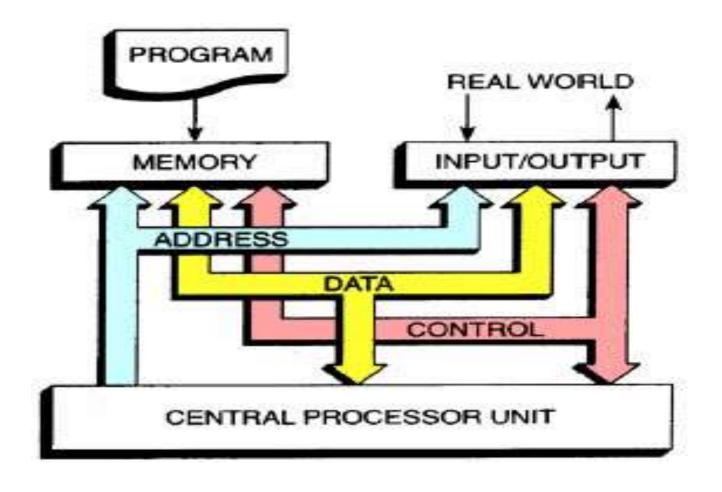

## PLC Principle/Operation

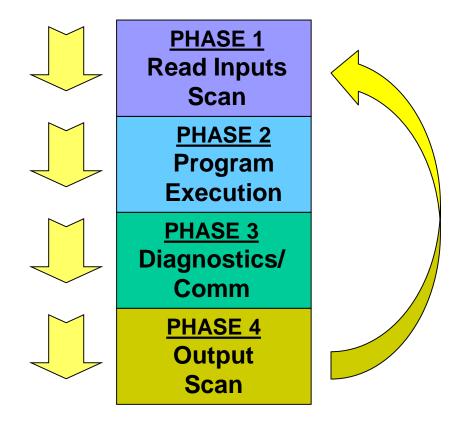

- Read all field input devices via the input interfaces, execute the user program stored in application memory, then, based on whatever control scheme has been programmed by the user, turn the field output devices on or off, or perform whatever control is necessary for the process application.

- This process of sequentially reading the inputs, executing the program in memory, and updating the outputs is known as scanning.

# **PLC** Operation

#### PHASE 1 – Input Status scan

- A PLC scan cycle begins with the CPU reading the status of its inputs.

PHASE 2– Logic Solve/Program Execution

- The application program is executed using the status of the inputs

PHASE 3– Logic Solve/Program Execution

- Once the program is executed, the CPU performs diagnostics and communication tasks

#### **PHASE 4 - Output Status Scan**

An output status scan is then performed, whereby the stored output values are sent to actuators and other field output devices. The cycle ends by updating the outputs.

#### **PLC** Operation

- As soon as Phase 4 are completed, the entire cycle begins again with Phase 1 input scan.

- The time it takes to implement a scan cycle is called SCAN TIME.

- The scan time composed of the program\_scan time, which is the time required for solving the control program, and the I/O update time, or time required to read inputs and update outputs.

- The program scan time generally depends on the amount of memory taken by the control program and type of instructions used in the program. The time to make a single scan can vary from 1 ms to 100 ms

While the PLC is running, the scanning process includes the following four phases, which are repeated continuously as individual cycles of operation:

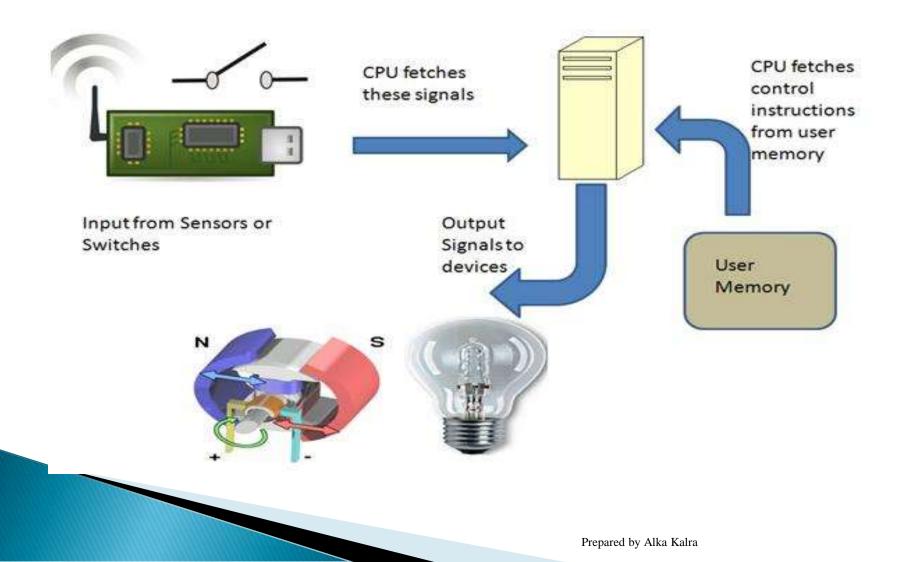

#### PLC WORKING

# PLC WORKING

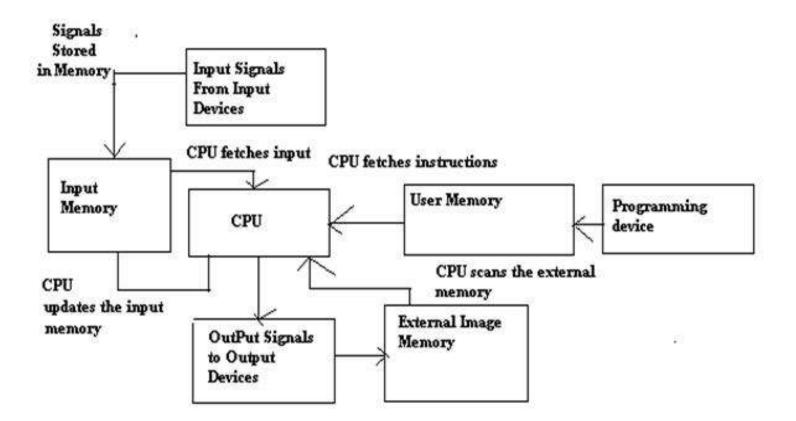

- The input sources convert the real-time analog electric signals to suitable digital electric signals and these signals are applied to the PLC through the connector rails.

- These input signals are stored in the PLC external image memory in locations known as bits. This is done by the CPU

- The control logic or the program instructions are written onto the programming device through symbols or through mnemonics and stored in the user memory.

# PLC WORKING

- The CPU fetches these instructions from the user memory and executes the input signals by manipulating, computing, processing them to control the output devices.

- The execution results are then stored in the external image memory which controls the output drives.

- The CPU also keeps a check on the output signals and keeps updating the contents of the input image memory according to the changes in the output memory.

- The CPU also performs internal programming functions like setting and resetting of the timer, checking the user memory.

## **PLC** Working

#### **PLC** Architecture

# PLC Modules

- PLCs are capable of monitoring the inputs continuously from sensors and producing the output decisions to operate the actuators based on the program. Every PLC system needs at least these three modules:

- CPU Module

- Power Supply Module

- One or more I/O Module

#### **CPU/Procssor** module

CPU module consists of a central processor and its memory. The Processor is responsible for doing all the necessary computations and data processing by accepting the inputs and producing appropriate outputs.

# Function of CPU/Processor

- The main function of the microprocessor is to analyze data coming from field sensors through input modules, make decisions based on the user's defined control program and return signal back through output modules to the field devices.

- Field sensors(Input): switches, flow, level, pressure, temp. transmitters, etc.

- Field output devices: motors, valves, solenoids, lamps, or audible devices.

#### **Memory Structures**

- These PLCs use retentive memory to save user programs and data when the power supply breaks or fails and to resume the execution of a user program ones the power is restored.

- Thus, these PLCs do not need any use of a keyboard or monitor for re programming the processor each time.

- The retentive memory can be implemented with the use of long-life batteries, EEPROM modules and flash memory methods.

# Memory Structures/Designs

#### VOLATILE.

- A volatile memory is one that loses its stored information when power is removed.

- Even momentary losses of power will erase any information stored or programmed on a volatile memory chip.

- Common Type of Volatile Memory

- **RAM.** Random Access Memory(Read/Write)

## RAM

- Read/write indicates that the information stored in the memory can be retrieved or read, while write indicates that the user can program or write information into the memory.

- The words random access refer to the ability of any location (address) in the memory to be accessed or used. Ram memory is used for both the user memory (ladder diagrams) and storage memory in many PLC's.

#### **CMOS-RAM Memory**

- The CMOS-RAM (Complimentary Metal Oxide Semiconductor) is probably one of the most popular. CMOS-RAM is popular because it has a very low current drain when not being accessed (15microamps), and the information stored in memory can be retained by as little as 2Vdc.

- RAM memory must have battery backup to retain or protect the stored program.

# Memory Design

#### NON-VOLATILE

- Has the ability to retain stored information when power is removed, accidentally or intentionally. These memories do not require battery back-up.

- Common Type of Non-Volatile Memory

- **ROM, Read Only Memory**

- Read only indicates that the information stored in memory can be read only and cannot be changed. Information in ROM is placed there by the manufacturer for the internal use and operation of the PLC.

### **Non-Volatile Memory**

- **PROM, Programmable Read Only Memory**

- Allows initial and/or additional information to be written into the chip.

- PROM may be written into only once after being received from the PLC manufacturer; programming is accomplish by pulses of current.

- The current melts the fusible links in the device, preventing it from being reprogrammed. This type of memory is used to prevent unauthorized program changes.

# Non Volatile Memory

- **EPROM, Erasable Programmable Read Only Memory**

- Ideally suited when program storage is to be semipermanent or additional security is needed to prevent unauthorized program changes.

- The EPROM chip has a quartz window over a silicon material that contains the electronic integrated circuits. This window normally is covered by an opaque material, but when the opaque material is removed and the circuitry exposed to ultra violet light, the memory content can be erased.

- The EPROM chip is also referred to as **UVPROM**.

## **EEPROM Memory**

- Electrically Erasable Programmable Read Only Memory

- Also referred to as E<sup>2</sup>PROM, is a chip that can be programmed using a standard programming device and can be erased by the proper signal being applied to the erase pin.

- EEPROM is used primarily as a non-volatile backup for the normal RAM memory. If the program in RAM is lost or erased, a copy of the program stored on an EEPROM chip can be down loaded into the RAM.

## Memory

- Processor module includes both ROM and RAM memories.

- ROM (Program Memory/System Memory) contains the operating system, driver and application programs,

- RAM (Data Memory/Application Memory)stores userwritten programs and working data.

- The program information or the control logic is stored in the user memory or the program memory from where the CPU fetches the program instructions.

- The input and output signals and the timer and counter signals are stored in the input and output external image memory respectively.

#### **Memory Map Organization**

#### SYSTEM

#### **APPLICATION**

Data TableUser Program

•System memory includes an area called the EXECUTIVE, composed of permanently-stored programs that direct all system activities, such as execution of the users control program, communication with peripheral devices, and other system activities.

•The system memory also contains the routines that implement the PLC's instruction set, which is composed of specific control functions such as logic, sequencing, timing, counting, and arithmetic.

•System memory is generally built from read-only memory devices.

•The application memory is divided into the data table area and user program area.

•The data table stores any data associated with the user's control program, such as system input and output status data, and any stored constants, variables, or preset values. The data table is where data is monitored, manipulated, and changed for control purposes.

•The user program area is where the programmed instructions entered by the user are stored as an application control program.

#### **BUS or Rack**

- In some modular PLCs bus or rack is provided in the backplane of the circuit into which all the modules like CPU and other I/O modules are plugged to the corresponding slots.

- This bus enables the communication between CPU and I/O modules to send or receive the data.

- This communication is established by addressing the I/O modules according to the location from CPU module along the bus.

### **BUS or Rack**

- Suppose, if the input module is located in the second slot,

- the address must be I2:1.0 (second slot first channel only as an example).

- Some buses provide necessary power to I/O module circuitry, but they do not provide any power to sensors and actuators connected to I/O modules

# I/O Structures/Modules

- The I/O interface section of a PLC connects it to external field devices.

- The input and out modules of the programmable logic controller are used to connect the sensors and actuators to the system to sense the various parameters such as temperature, pressure and flow, etc.

- These I/O modules are of two types: digital or analog.

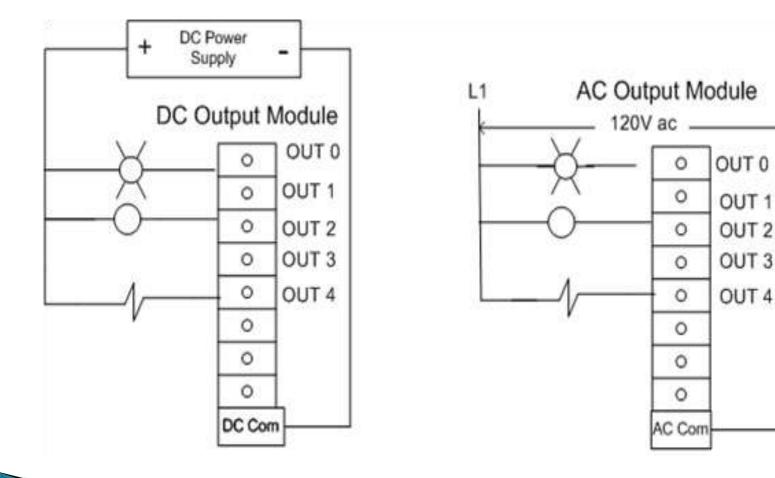

### I/O interface

- The main purpose of the I/O interface is to condition the various signals received from or sent to the external input and output devices.

- Input modules converts signals from discrete or analog input devices to logic levels acceptable to PLC's processor.

- Output modules converts signal from the processor to levels capable of driving the connected discrete or analog output devices.

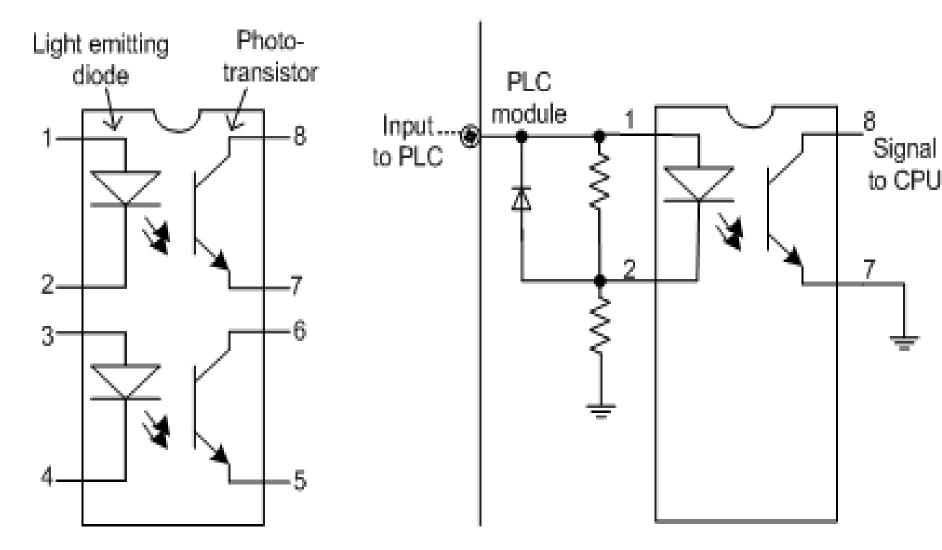

## I/O Structure/MODULE

Figure 1.6a Dual-optocoupler IC in 8-pin DIP

Figure 1.6b Basic DC input circuit

Prepared by Alka Kalra

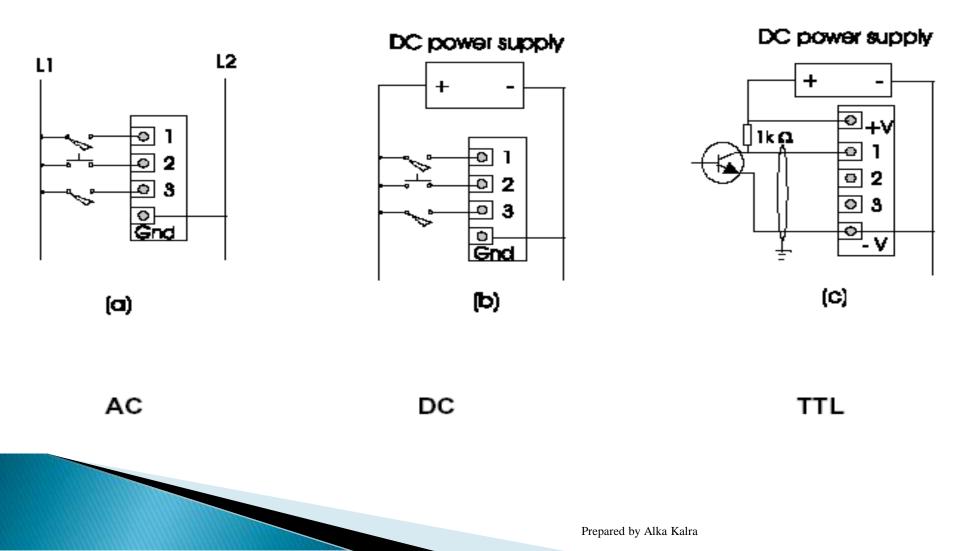

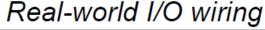

#### Input Connections

#### **DC/AC Output Wiring Connections**

L2

#### **DIFFERENT TYPES OF I/O Structures**

Pilot Duty Outputs

Outputs of this type typically are used to drive high-current electromagnetic loads such as solenoids, relays, valves, and motor starters.

These loads are highly inductive and exhibit a large current.

#### General - Purpose Outputs

- These are usually low- voltage and low-current and are used to drive indicating lights and other non-inductive loads.

- Noise suppression may or may not be included on this types of modules.

#### Discrete Inputs

- Circuits of this type are used to sense the status of limit switches, push buttons, and other discrete sensors.

- Noise suppression is of great importance in preventing false indication of inputs turning on or off because of noise.

#### Analog I/O Circuits

- Circuits of this type sense or drive analog signals.

- Analog inputs come from devices, such as thermocouples, strain gages, or pressure sensors, that provide a signal voltage or current that is derived from the process variable.

- Standard Analog Input signals: 4-20mA; 0-10V

- Analog outputs can be used to drive devices such as voltmeters, X-Y recorders, servomotor drives, and valves through the use of transducers.

- Standard Analog Output signals: 4-20mA; 0-5V; 0-10V

### Special - Purpose I/O

- Circuits of this type are used to interface PLCs to very specific types of circuits such as servomotors, stepping motors PID (proportional plus integral plus derivative) loops, high-speed pulse counting, resolver and decoder inputs, multiplexed displays, and keyboards.

- This module allows for limited access to timer and counter presets and other PLC variables without requiring a program loader.

#### **PROGRAMMING DEVICE**

- It is used to enter the desired program that will determine the sequence of operation and control of process equipment or driven machine.

- Also known as:

- Industrial Terminal (Allen Bradley)

- Program Development Terminal (General Electric)

- Programming Panel (Gould Modicon)

- Programmer (Square D)

- Program Loader (Idec-Izumi)

- Programming Console (Keyence / Omron)

#### **PROGRAMMING DEVICE TYPES**

- Various types of programming devices are used to enter, modify and troubleshoot a PLC program.

- Hand held unit with LED / LCD display

- Personal Computer (PC)

- Desktop type with a CRT display /Desktop Console

Hand held unit with LED / LCD display

- In the handheld programming device method, a proprietary device is connected to PLC through a connecting cable.

- This device consists of a set of keys that allows to enter, edit and dump the code into the PLC.

- These handheld devices consist of small display to make the instruction that has been programmed visible.

- These are compact and easy to use devices, but these handheld devices have limited capabilities.

## Desktop consoles

- Desktop consoles are likely to have a visual display unit with a full keyboard and screen display.

- Keyboard and monitor are used for programming.

- Programming Unit communicated with PLC through serial or Parallel port.

# Personal Computer(PC)

- PC is used for programming the PLC in conjunction with the software given by the manufacturer.

- By using this PC we can run the program in either online or offline mode, and can also edit, monitor, diagnose and troubleshoot the program of the PLC.

- The way of transferring the program to the PLC is shown in the above figure wherein the PC consists of program code corresponding to control application which is transferred to the PLC CPU via programming cable.

- . A major advantage of using a computer is that the program can be stored on the hard disk or a CD and copies can be easily made.

#### PLC Communications Ports Application/Use

Changing resident PLC programs uploading/downloading from a supervisory controller (Laptop or desktop computer).

• Forcing I/O points and memory elements from a remote terminal.

Linking a PLC into a control hierarchy containing several sizes of PLC and computer.

Monitoring data and alarms, etc. via printers or Operator Interface Units (OIUs).

#### PLC Communications Standards

#### **RS 232**

Used in short-distance computer communications, with the majority of computer hardware and peripherals. Has a maximum effective distance of approx. 30 m at 9600 baud.

#### RS 422 / RS 485

Used for longer-distance links, often between several PCs in a distributed system. RS 485 can have a maximum distance of about 1000 meters.

# Local Area Network(LAN)

Local Area Network provides a physical link between all devices plus providing overall data exchange management or protocol, ensuring that each device can "talk" to other machines and understand data received from them.

- LANs provide the common, high-speed data communications bus which interconnects any or all devices within the local area.

- LANs are commonly used in business applications to allow several users to share costly software packages and peripheral equipment such as printers and hard disk storage.

#### **Power Supply Module**

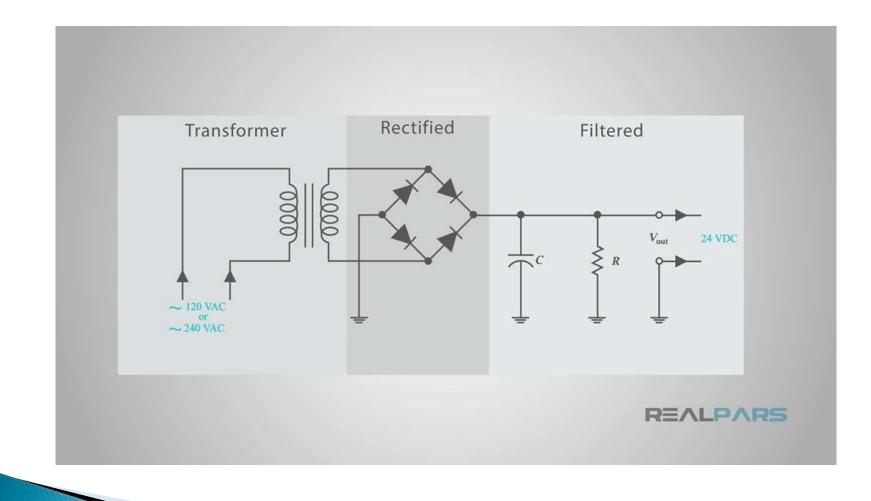

- A PLC power supply is the workhorse of the PLC system. It converts your line voltage, 120 or 240 volts AC, to a lower DC voltage, commonly 24 volts DC. This DC voltage is then sent into the rack to power the rest of the PLC components.

- The output 5V DC drives the computer circuitry, and in some PLCs 24DC on the bus rack drives few sensors and actuators.

## **PLC Power Supply**

# **PLC Power Supply**

- Line voltage is stepped down with a transformer, rectified to convert it to DC, filtered with capacitors, and protected during this process. All of this is packed into that small looking power supply.

- This DC voltage is used to power the rest of the PLC and components.

- The common current ratings for PLC's are anywhere from 2 to 10 amps for smaller systems and up to 50 amps for larger, more powerful controllers.

Criteria for Selection a PLC/Specifications

Number of logical inputs and outputs

This specifies the number of I/O devices that can be connected to the controller.

There should be sufficient I/O ports to meet present requirements with enough spares to provide for moderate future expansion.

#### Specifications

#### MEMORY CAPACITY

The amount of memory required for a particular application is related to the length of the program and the complexity of the control system.

- Simple applications having just a few relays do not require significant amount of memory.

- Program length tend to expand after the system have been used for a while.

- It is advantageous to a acquire a controller that has more memory than is presently needed.

# Specifications

#### OUTPUT-PORT POWER RATINGS

Each output port should be capable of supplying sufficient voltage and current to drive the output peripheral connected to it.

#### Scan Time

This is the speed at which the controller executes the relay ladder logic program. This variable is usually specified as the scan time per 1000 logic nodes and typically ranges from 1 to 200 milliseconds.

#### **PLC Communications**

#### **Programmable Controllers and Networks**

Dedicated Network System of Different Manufacturers

| Manufacturer      | Network            |

|-------------------|--------------------|

| Allen-Bradley     | Data Highway       |

| Gould Modicon     | Modbus             |

| General Electric  | GE Net Factory LAN |

| Mitsubishi        | Melsec-NET         |

| Square D          | SY/NET             |

| Texas Instruments | TIWAY              |

## Specifications

#### Communications Port

#### > RS-232, RS 422 / RS 485,LAN

#### ➢Software

- 1. Allen-Bradley Rockwell Software RSLogix500

- 2. Modicon Modsoft

- 3. Omron Syswin

- 4. GE-Fanuc Series 6 LogicMaster6

- 5. Square D- PowerLogic

- 6. Texas Instruments Simatic

- 6. Telemecanique Modicon TSX Micro

# Practical Design Approach

#### A Detailed Design Process

- 1. Understand the process

- 2. Hardware/software selection

- 3. Develop ladder logic

- 4. Determine scan times and memory requirements

#### **PLC Status Indicators**

- 1. Power On

- 2. Run Mode

- 3. Programming Mode

- 4. Fault

#### **Troubleshooting PLC System**

- 1. Look at the process

- 2. PLC status lights

- HALT something has stopped the CPU

- RUN the PLC thinks it is OK (and probably is)

- ERROR a physical problem has occurred with the PLC

- 3. Indicator lights on I/O cards and sensors

- 4. Consult the manuals, or use software if available.

- 5. Use programming terminal / laptop.

#### **Chapter 3** Ladder Diagram Programming

## Basic Instruction Example-1

- Problem Statement :

- Providing lubricant for the gear box before the lathe spindle starts to run which aims to ensure that the oil pump motor starts first and the main motor starts subsequently.

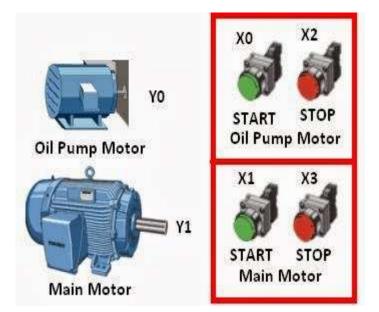

#### Number of PLC Inputs Required

- X0 START pushbutton to Start Oil Pump Motor

- X1 START pushbutton to Stop Main Motor

- X2 STOP pushbutton to Stop Oil Pump Motor

- X3 STOP pushbutton to Stop Main Motor

- Number of PLC Outputs Required

- Y0 Oil Pump Motor

- Y1 Main Motor

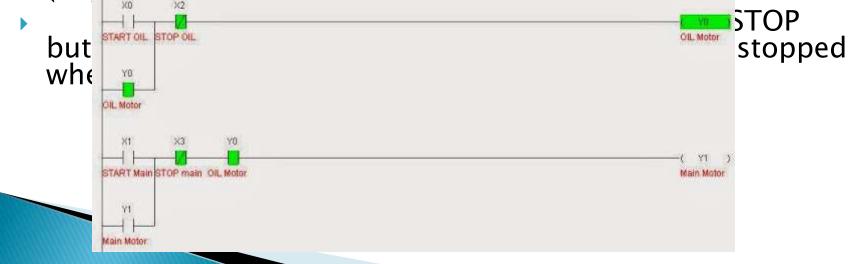

#### PLC Ladder Programming Description

This program is a typical application of the conditional control circuit.

Y0 = ON when Oil Pump START button is pressed.

Therefore, the oil pump will start to provide lubricant for the gear box of main motor(Y1)

- Under the precondition of the operating state of the Oil pump, the main motor (Y1) will be ON when the Main motor START button is pressed.

- During the operation of main motor (Y1), oil pump (Y0) needs to provide lubricant continuously.

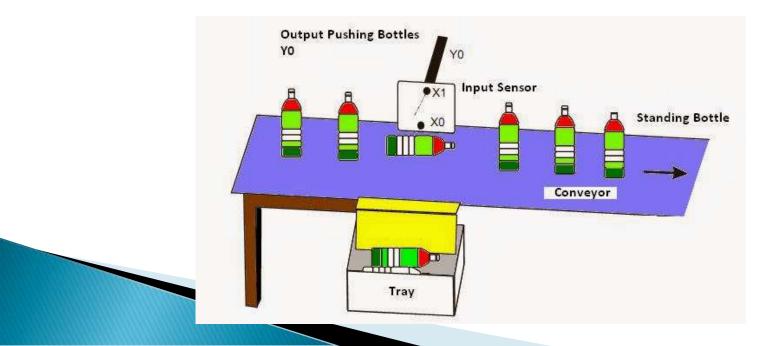

### Basic Instruction Example-2

Problem Statement: Detecting the standing bottles on the conveyor and pushing falling bottles in tray.

# Ladder Program

#### Number of PLC Inputs Required

XO - Proximity Sensor to sense bottom of the Bottle i.e. <math>XO = ON when the detected input signal from the bottle-bottom is sheltered.

X1 – Proximity Sensor to sense upper part of the Bottle i.e. X1 = ON when the detected input signal from the bottle-neck is sheltered. <u>Number of PLC Outputs Required</u>

Y0 - To operate Pushing Cylinder/Rod

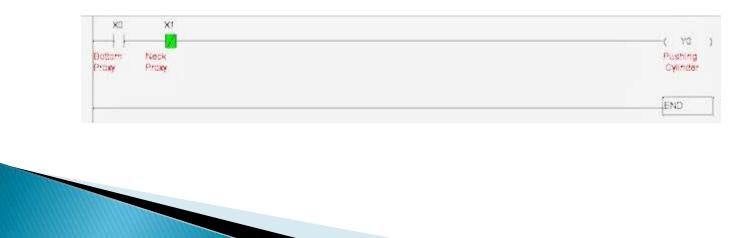

## **Program Description**

- If the bottle on the conveyor belt is upstanding, the input signal from monitoring photocell at both bottle-bottom and bottleneck will be detected. In this case, X0 = ON, and X1 = ON. The normally open (NO) contact X0 will be activated as well as the normally closed (NC) contact X1. Y0 remains OFF and pneumatic pushing pole will not perform any action.

- If the bottle from the conveyor belt is down, only the input signal from monitoring photocell at the bottle-bottom will be detected. In this case, X0 = ON, X1 = OFF. The state of output YO will be ON because the NO contact X0 activates and the NC contact X1 remains OFF. The pneumatic pushing pole will push the fallen bottle out of the conveyor belt.

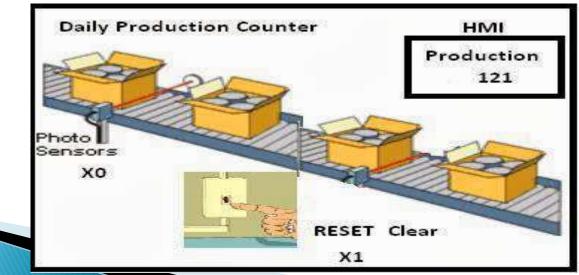

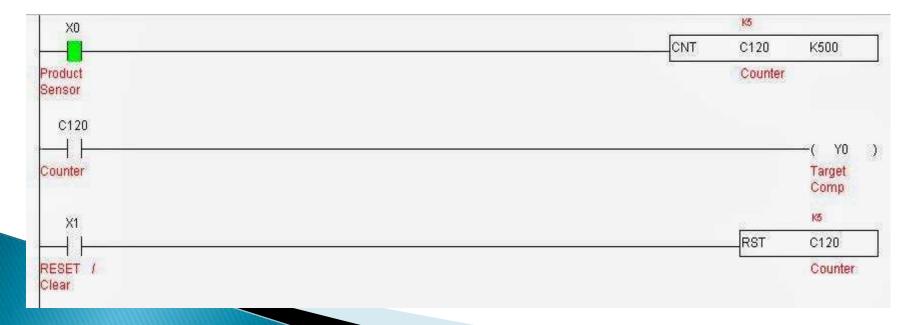

#### Counter Programming Example

#### PLC Ladder Practice Problem:

The production line may be powered off accidentally or turned off for noon break. The program is to control the counter to retain the counted number and resume counting after the power is turned ON again. When the daily production reaches 500, the target completed indicator will be ON to remind the operator for keeping a record. Press the Clear button to clear the history records. The counter will start counting from 0 again.

### **UP counter Example**

#### Latched 16 bit UP counter

- Number of PLC Inputs Required

- X0 Product Detecting Sensor. X1 Production Counter RESET/Clear

- Number of PLC Outputs Required

Y0 Production Counter Target Completed.

- Number of PLC Counter Required:

C120 16 Bit Latched Counter. (Max Count = 32,768)

## **Program Description**

- The latching counter is demanded for the situation of retaining data when power-off.

- When a product is completed, C120 will count for one time. When the number reaches 500, target completed indicator Y0 will be ON.

- For different series of PLC, the setup range of 16-bit latching counter is different.

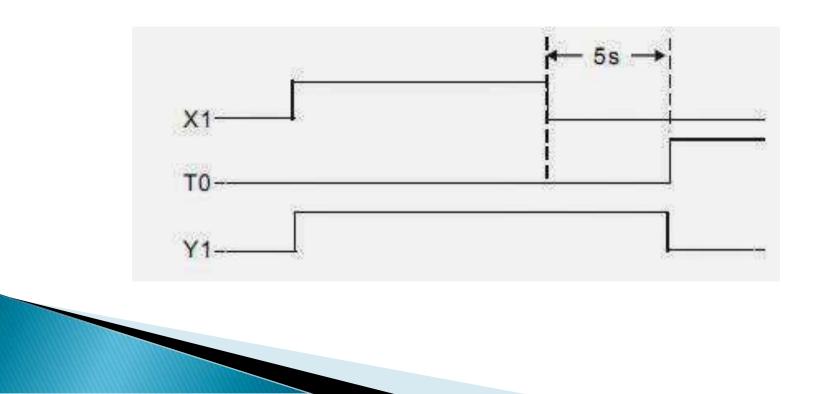

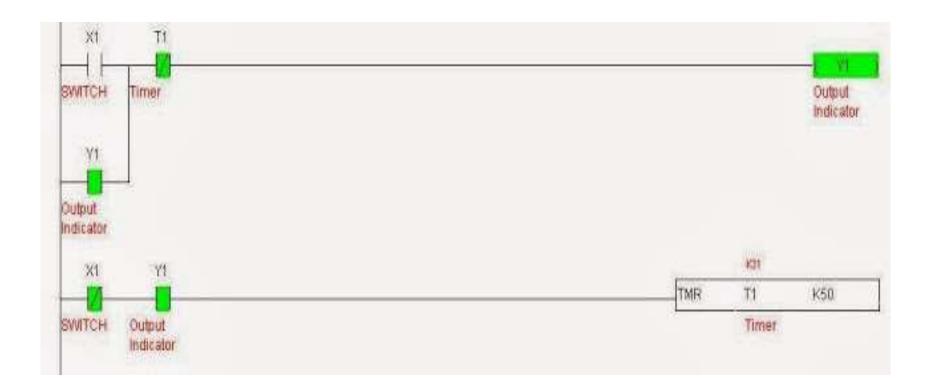

### Timer Programming Example

Enabling the indicator to be ON immediately when switch pressed and OFF after a 5 sec delay by the switch.

#### PLC Ladder Program Description

- Number of PLC Inputs Required

- X1 Start Switch.

- Number of PLC Outputs Required

- Y1 Output Indicator

- Number of PLC Timer Required

- T0 5 second Timer, 100 ms Time Base. (See K50 Preset Value for Timer)

When X1 = ON, TMR instruction will be executed. Timer T1 will be ON and start counting for 3 sec. When T1 reaches its set value, the NO (Normally Open) contact T1 will be activated and indicator YI will be ON. When X1 = OFF, TMR instruction will not be executed. Timer T1 will be OFF and so will NO contact T1. Therefore, the indicator Y1 will be OFF.

#### Ladder Program

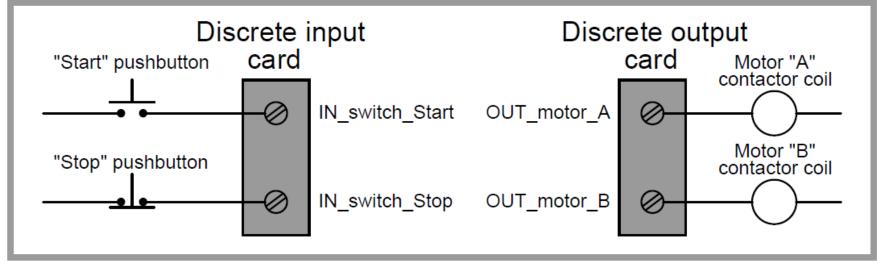

#### **Comparison Instruction Example**

A practical application for a comparative function is something called alternating motor control, where the runtimes of two redundant electric motors are monitored, with the PLC determining which motor to turn on next based on which motor has run the least

#### Description

- In this program, two retentive on-delay timers keep track of each electric motor's total run time, storing the run time values in two registers in the PLC's memory:

- Motor A runtime and Motor B runtime. These two integer values are input to the "greater than" instruction box for comparison.

- If motor A has run longer than motor B, motor B will be the one enabled to start up next time the "start" switch is pressed.

- If motor A has run less time or the same amount of time as motor B (the scenario shown by the blue-highlighted status indications), motor A will be the one enabled to start.

- The two series-connected virtual contacts OUT motor A and OUT motor B ensure the comparison between motor run times is not made until both motors are stopped.

- If the comparison were continually made, a situation might arise where both motors would start if someone happened to press the Start pushbutton with one motor is already running.

#### Ladder Program

PLC program

# **CHAPTER 4** Applications of PLCs

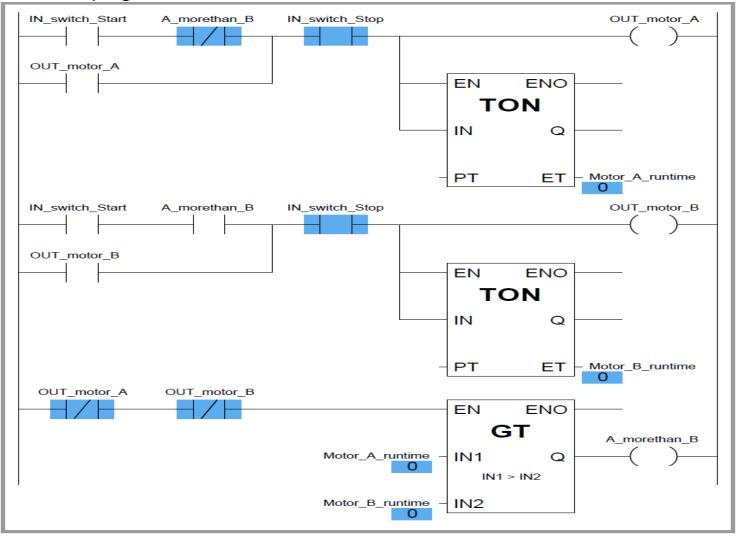

#### Automation of product packaging

- Product packaging is one of the most frequent cases for automation in industry.

- It can be encountered with small machines (ex. packaging grain like food products) and large systems such as machines for packaging medications.

- Example we are showing here solves the classic packaging problem with few elements of automation.

#### Automation of product packaging

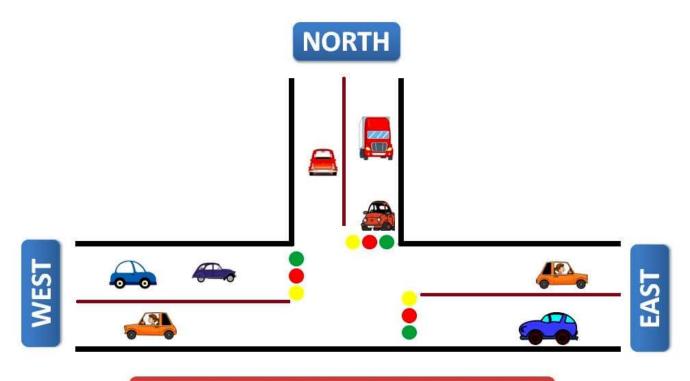

# Three WayTraffic Light Control using PLC

#### 3 - Way Traffic Light Control using PLC

InstrumentationTools.com

#### Traffic Light Control using PLC

| S.no | Address | Name         | Input/Output |

|------|---------|--------------|--------------|

| 1    | I:0/0   | Start        | Input        |

| 2    | I:0/1   | Stop         | Input        |

| 3    | B3.0    | Memory       | Memory       |

| 4    | O:0/0   | West Green   | Output       |

| 5    | O:0/1   | East Red     | Output       |

| 6    | O:0/2   | North Red    | Output       |

| 7    | O:0/3   | East yellow  | Output       |

| 8    | O:0/4   | East Green   | Output       |

| 9    | O:0/5   | West Red     | Output       |

| 10   | O:0/6   | North Yellow | Output       |

| 11   | O:0/7   | North Green  | Output       |

| 12   | O:1/0   | West Yellow  | Output       |

#### Traffic Light Control using PLC

- They are so many ways to write a program for traffic light control ex: sequencer output method but in this normal input, outputs and timers are used.

- Timers are used to give time delay for output to turn ON and OFF.

- Reset coil is used at the end to run the program continuously.

- Comparator blocks are used to reduce the number of timers used.

#### Steps or sequence of outputs to turn ON

| S.NO | EAST | WEST | NORTH |

|------|------|------|-------|

| 1    | R    | G    | R     |

| 2    | Y    | G    | R     |

| 3    | G    | R    | R     |

| 4    | G    | R    | Y     |

| 5    | R    | R    | G     |

| 6    | R    | Y    | G     |

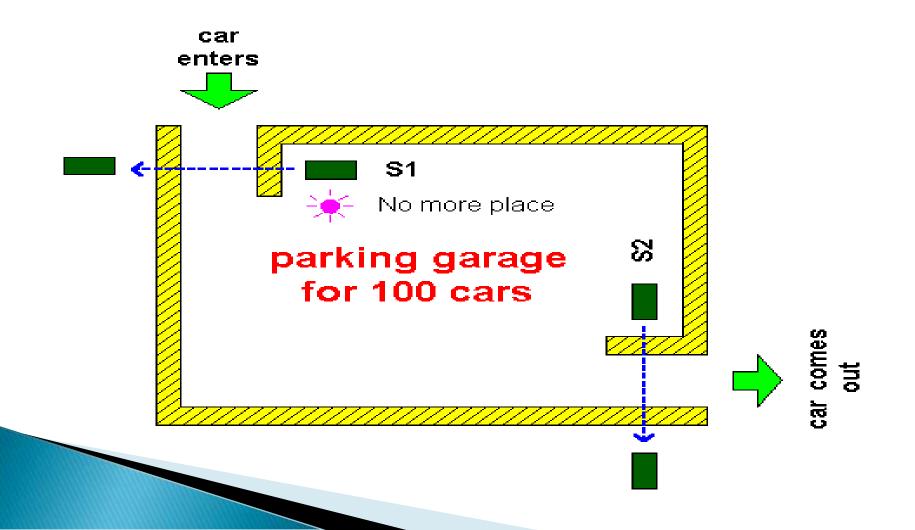

## **Car Parking System**

We are dealing with a simple system that can control 100 car at the maximum. Each time a car enters, PLC automatically adds it to a total sum of other cars found in the garage. Each car that comes out will automatically be taken off. When 100 cars park, a signal will turn on signalizing that a garage is full and notifying other drivers not to enter because there is no space available.

#### Automation of parking garage

# PLC ladder logic for washing machine

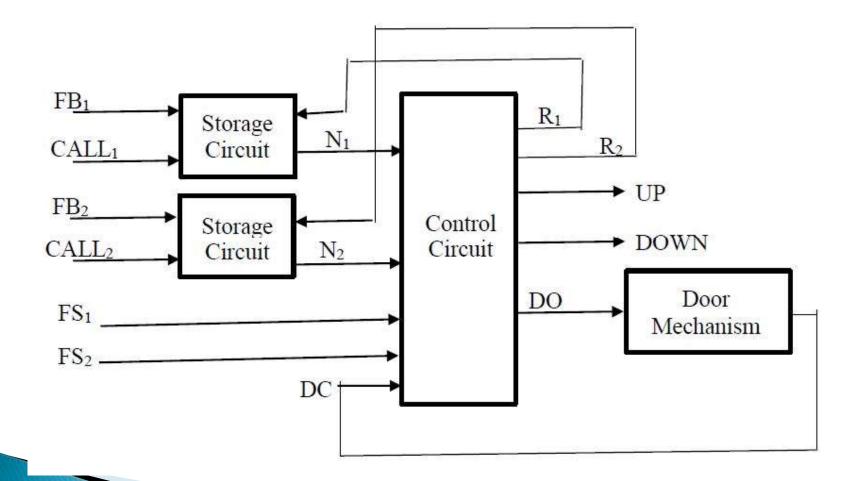

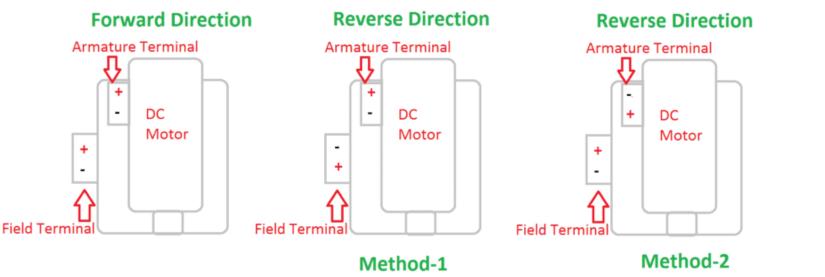

#### Forward & Reverse of DC motor:

DC motors are totally different from AC motors. They have commutator, field winding and armature winding. The DC supply will be given to the field winding and armature winding. You can reverse the direction for DC motor in two ways.

## Forward & Reverse of DC motor

#### **DC Motor Forward and Reverse Direction**

(Changing Field Polarity) (Changing Aramature polarity)

#### Forward & Reverse of DC motor

- By changing the supply Polarity in field winding or filed supply. Field terminal consist of F1 and F2. Normally, in forward direction the DC supply will be given such as F1 – Positive and F2 – Negative, to change the direction the polarity should be F1 – Negative and F2 – Positive.

- Also in same way we can change the direction of DC Motor by changing the polarity of the armature winding. Armature terminal consist of A1 and A2. Normally, for forward direction the DC supply will be given such as A1 – Positive and A2 – Negative, to change the direction the polarity should be A1 – Negative and A2 – Positive.

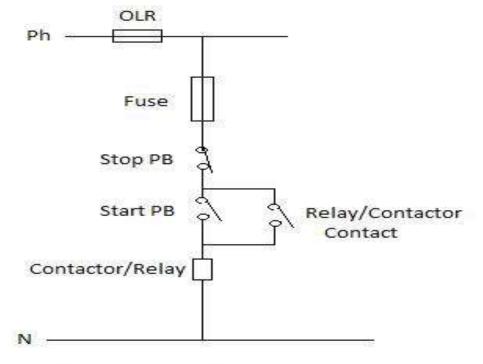

### Direct-On-Line (DOL) starter

One method of starting electric motors is using direct on line (DOL) or across the line starter. In this method full line voltage is applied to the motor terminals. This is simplest type of motor starter.

#### **DOL Starter**

DOL motor starter contains fuse and over load relay (OLR) for protection purpose. The starter can be contain momentary contact or maintained contact push buttons. The example considered here is momentary contact push buttons. For starting purpose normally open (NO) push button is preferred whereas normally closed (NC) push button is used to stop the motor.

The excessive supply voltage drop causing high inrush current is the criteria to limit the use of DOL starter. Conveyor motors, water pumps are the applications where DOL starters are used.

#### **DOL Starter**

Control Circuit for DOL Starter

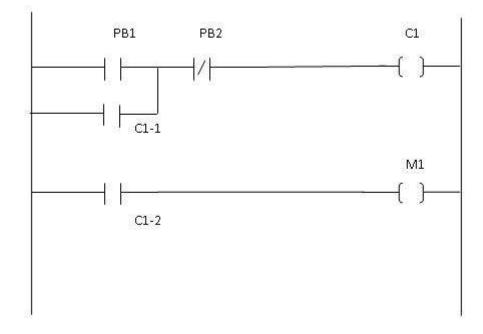

### Sequence of Events

Listing of Input and Output devices: Inputs: PB1 – To start the motor PB2 – To stop the motor Output: M1 – Motor

1. When Start push button (PB1) is pressed, Motor (M1) has to start.

2. If Start pushbutton (PB1) is released and Stop pushbutton (PB2) is not pressed, Motor (M1) should remain on.

3. When Stop push button (PB2 is pressed, Motor (M1) has tol stop.

4. If stop push button is released and start is not pressed (released) motor should remain off.

#### **DOL Starter**

# **CHAPTER 5** Introduction to SCADA

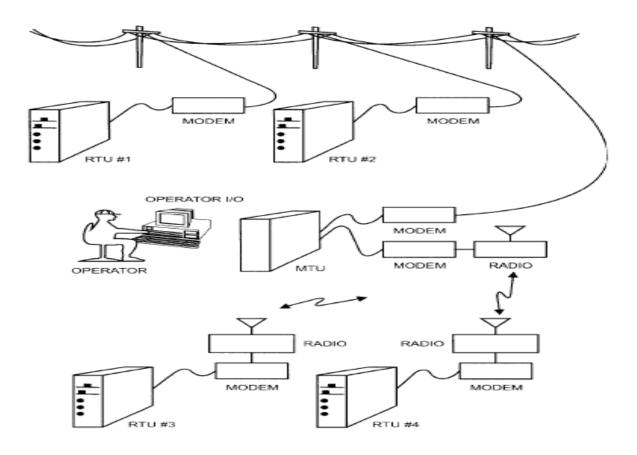

## SCADA

- SCADA is the acronym for Supervisory Control And Data Acquisition. It is generally used for industrial control systems.

- Thus, it is not a comprehensive control system but it rather operates as supervisory software superior to PLCs and other devices.

## SCADA system

- A SCADA system is a common process automation system which is used to gather data from sensors and instruments located at remote sites and to transmit and display this data at a central site for control or monitoring purposes.

- Common analog signals that SCADA systems monitor and control are levels, temperatures, pressures, flow rate and motor speed. Typical digital signals to monitor and control are level switches, pressure switches, generator status, relays & motors.

- The collected data is usually viewed on one or more SCADA Host computers located at the central or master site.

## Features of SCADA

- 1. Analog inputs for live monitoring

- Analog inputs allow you to monitor real-time data across your network.

- Many SCADA systems will only have discrete inputs – which are digital and can only tell you if something is "on" or "off."

- An analog input will be able to tell you precise values, meaning you can have accurate data about whatever you're monitoring.

- Graphical web interface is used for easy-to-use interface system of SCADA

# Control relays for remote access and control

- By having control relays on your SCADA system, you'll be able to remotely control any device in your network that is normally operated by a button or a switch.

- You'll be able to start equipment, open or close doors, or turn on lights.

- Instead of driving long distances to perform these simple tasks, you can do them right from your desk – without wasting time or money behind the windshield of a truck.

## **Functions of SCADA**

All the equipment connected through machine control are operated through instruction sent over the web. The processing unit analyses the data and supervises the healthy functioning of the signals transmitted in the entire unit. The data is stored for valuation in a distributed database. The acquired data also has reference metadata stored for in the different database such as a programmable logic controller (PLC).

## How does it work?

The complete SCADA systems has four significant units namely – data communication, data acquisition, information or data presentation and monitoring and control system. With complete symphony in the above four mentioned units, the entire operation of the automation system can be monitored.

## How does it work?

The data acquisition system fetches real-time data from all the connected machine units. The data reports about the status of all the components and sensors, where data communication network comes into play. The system ensures accuracy in data being transferred through the internet protocol. Once the data is collected, the processing unit analyses the data and presents it to the operator through Human-Machine Interface (HMI).

## Scope of SCADA

- This is the reason why many more enterprises are looking for automating their industrial processes.

- With the Industrial Internet of Things taking the front seat, it is essential to look for companies helping businesses step towards automation. Schneider

- Electric India is one of the significant names in the research and development of the automation industry. It has not only brought these systems to common units but also helps the employees to up skill their knowledge by training them how to operate the machinery.

# Elements of a SCADA system

- ► HMI

- RTU

- MTU

- Data transmission

## Elements of a SCADA system

## HMI unit

A Human – Machine Interface (HMI) is the apparatus which presents process data to a human operator, and through this, the human operator monitor and control the process. HMI offers real-time monitor of data about the process and through which an operator can send commands to the controller. Input devices such as the keyboard, mouse, trackballs are available in this section.

## MTU:

- MTU (master control unit), which is the system controller. Some industries use the term "host computer" instead of MTU.

- MTU communicates with the RTU that is located away from the central location. There can be many RTUs in the field, MTU can monitor and control the field using the scheduled program even when the operator is not present. Changes can be done in the process from the MTU end, can read some process parameter.

## RTU

- Remote terminal unit (RTU) connection to sensors in the process and converting sensors signals to digital data and sending digital data to the supervisory system.

- RTU communicate with the MTU using modulated signal. RTU receives the modulated data from MTU and connection can be through cable or radio.

- RTU field device connection is through cables. RTU supplies both electrical power and actuator signal to the field device.

# **Advantages of SCADA**

- Long distance monitoring

- Long distance training

- Protection against terrorism/vandalism-alarm

- Data management (engineering and operations)

- Automated operations with real-time control

- Reliability and Robustness (very large installed base, mission-critical processes)

# **Application Of SCADA**

SCADA systems are used to control and monitor physical processes, examples of which are transmission of electricity, transportation of gas and oil in pipelines, water distribution, traffic lights, and other systems used as the basis of modern society.

## Application of the System

- Although this is a new technology, businesses have already leveraged the technology in both the public and private sector. It has brought about immense satisfaction in the operation managers because the system makes the production line foolproof.

- This also streamlines packaging and delivery lines following the processes. The overall automation and process control has helped to save a significant amount of money and time.

## SCADA Application Example

A real world SCADA system can monitor and control hundreds to hundreds of thousands of I/O points. A typical Water SCADA **application** would be to monitor water levels at various water sources like reservoirs and tanks and when the water level exceeds a preset threshold, activate the system of pumps to move water to tanks with low tank levels.

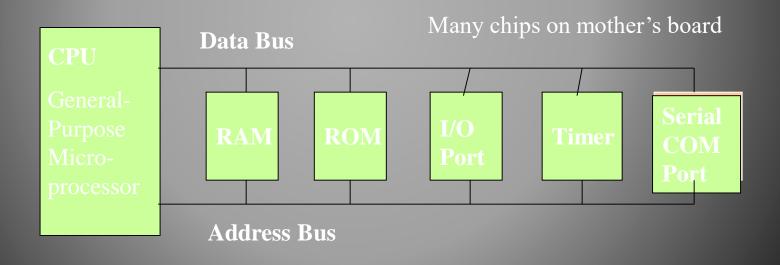

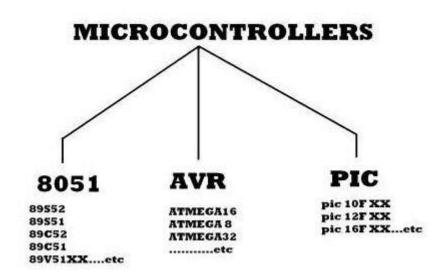

# CHAPTER 6 Micro Controller Series (MCS)–51 Over View

Why do we need to learn Microprocessors/controllers?

- The microprocessor is the core of computer systems.

- Nowadays many communication, digital entertainment, portable devices, are controlled by them.

- A designer should know what types of components he needs, ways to reduce production costs and product reliable.

- Hardware :Interface to the real world

- Software :order how to deal with inputs

# Elements of microprocessor/Microcontroller

- CPU: Central Processing Unit

- I/O: Input /Output

- Bus: Address bus & Data bus

- Memory: RAM & ROM

- Timer

- Interrupt

- Serial Port

- Parallel Port

### Microprocessors

#### General-purpose microprocessor

- CPU for Computers

- ▶ No RAM, ROM, I/O on CPU chip itself

- Example : Intel's 8085,8086, Motorola's 680x0

## Microprocessor vs. Microcontroller

#### Microprocessor

- CPU is stand-alone, RAM, ROM, I/O, timer are separate

- Designer can decide on the amount of ROM, RAM and I/O ports.

- expansive

- versatility

- general-purpose

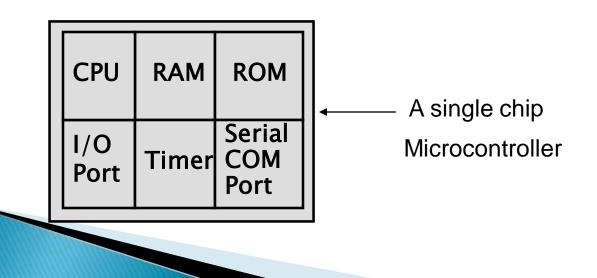

#### Microcontroller

- CPU, RAM, ROM, I/O and timer are all on a single chip

- fix amount of on-chip ROM, RAM, I/O ports

- for applications in which cost, power and space are critical

- single-purpose

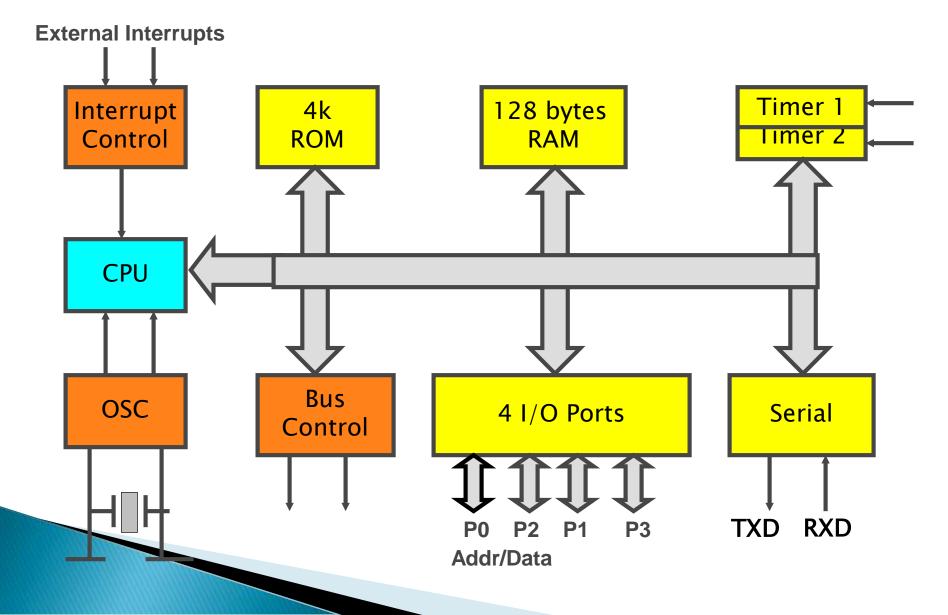

# 8051 Basic Component

- 4K bytes internal ROM

- 128 bytes internal RAM

- Four 8-bit I/O ports (P0 P3).

- Two 16-bit timers/counters

- One serial interface

# **Block Diagram**

# Other 8051 featurs

- only 1 On chip oscillator (external crystal)

- 6 interrupt sources (2 external, 3 internal, Reset)

- 64K external code (program) memory(only read)PSEN

- 64K external data memory(can be read and write) by RD,WR

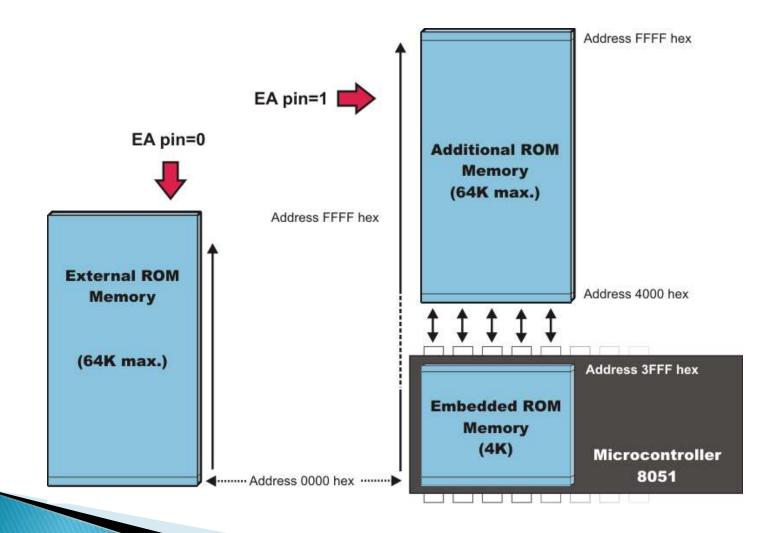

- Code memory is selectable by EA (internal or external)

We may have External memory as data and code

#### Comparison of the 8051 Family Members

| 89XX   | ROM | RAM | Timer | Int<br>Source | IO pin | Other |

|--------|-----|-----|-------|---------------|--------|-------|

| 8951   | 4k  | 128 | 2     | 6             | 32     | -     |

| 8952   | 8k  | 256 | 3     | 8             | 32     | -     |

| 8953   | 12k | 256 | 3     | 9             | 32     | WD    |

| 8955   | 20k | 256 | 3     | 8             | 32     | WD    |

| 898252 | 8k  | 256 | 3     | 9             | 32     | ISP   |

| 891051 | 1k  | 64  | 1     | 3             | 16     | AC    |

| 892051 | 2k  | 128 | 2     | 6             | 16     | AC    |

WD: Watch Dog Timer AC: Analog Comparator ISP: In System Programable

### Three criteria in Choosing a Microcontroller

- meeting the computing needs of the task efficiently and cost effectively

- speed, the amount of ROM and RAM, the number of I/O ports and timers, size, packaging, power consumption

- easy to upgrade

- cost per unit

- availability of software development tools

- assemblers, debuggers, C compilers, emulator, simulator, technical support

- wide availability and reliable sources of the microcontrollers

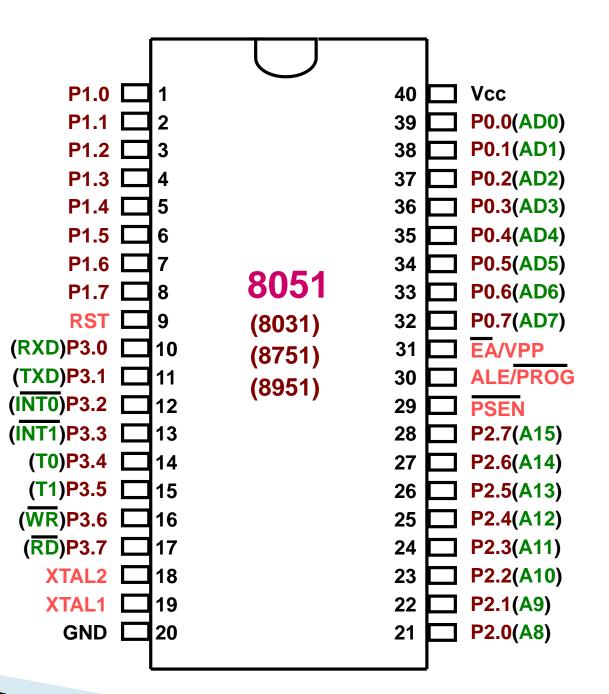

## 8051 Foot Print

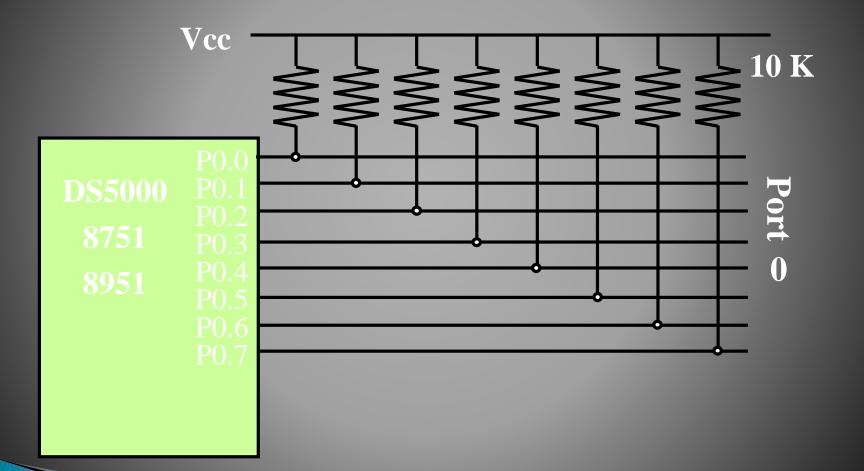

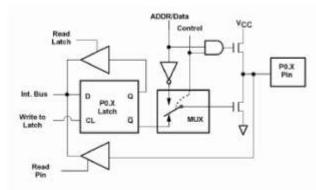

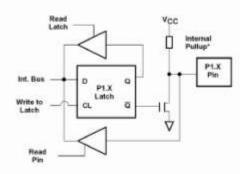

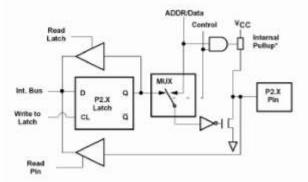

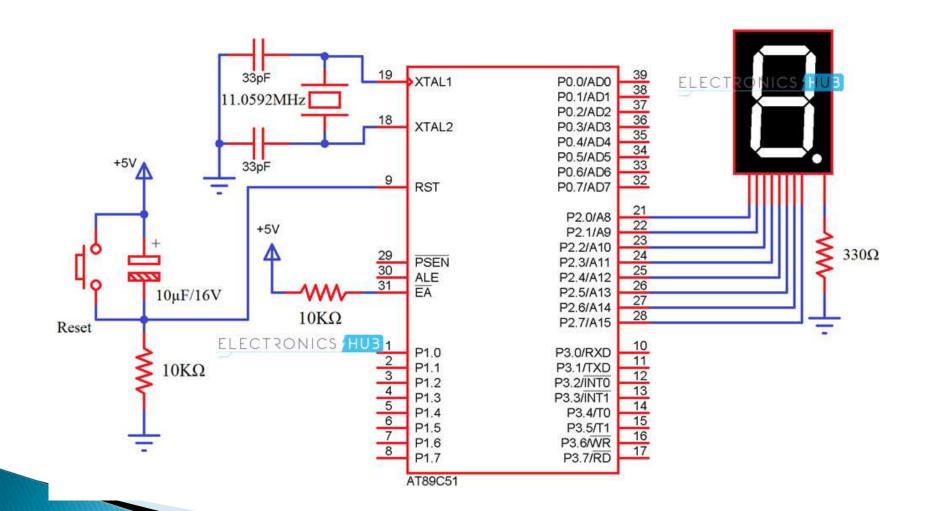

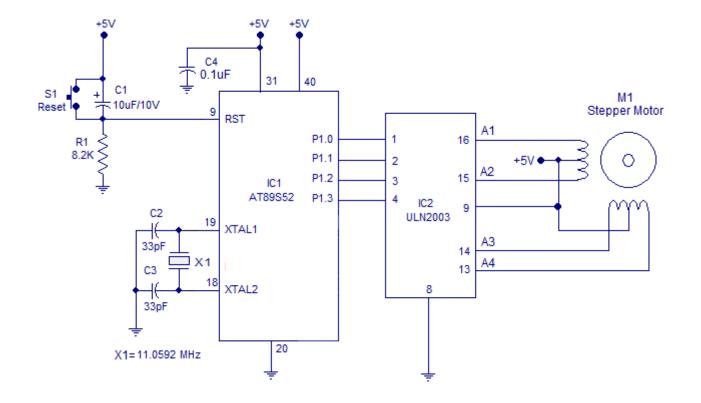

#### **IMPORTANT PINS (IO Ports)**

- One of the most useful features of the 8051 is that it contains four I/O ports (P0 - P3)

- ▶ Port 0 (pins 32–39) : P0 (P0.0~P0.7)

- 8-bit R/W General Purpose I/O

- Or acts as a multiplexed low byte address and data bus for external memory design

- ▶ Port 1 (pins 1-8) : P1 (P1.0~P1.7)

- Only 8-bit R/W General Purpose I/O

- ▶ Port 2 (pins 21–28) : P2 (P2.0~P2.7)

- 8-bit R/W General Purpose I/O

- Or high byte of the address bus for external memory design

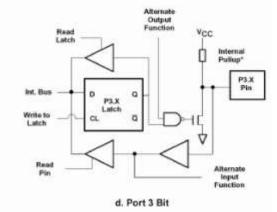

- ▶ Port 3 (pins 10–17) : P3 (P3.0~P3.7)

- General Purpose I/O

- if not using any of the internal peripherals (timers) or external interrupts.

- Each port can be used as input or output (bi-direction)

#### Pins of 8051

PSEN (out): Program Store Enable, the read signal for external program memory (active low).

ALE (out): Address Latch Enable, to latch address outputs at Port0 and Port2

EA (in): External Access Enable, active low to access external program memory locations 0 to 4K

**RXD,TXD**: UART pins for serial I/O on Port 3

XTAL1 & XTAL2: Crystal inputs for internal oscillator.

▶ Vcc (pin 40) :

Vcc provides supply voltage to the chip.

• The voltage source is +5V.

GND (pin 20) : ground

#### Pins of 8051

- RST (pin 9: Reset

- $\circ$  input pin and active high (normally low) .

- The high pulse must be high at least 2 machine cycles.

- Power–on reset

- Upon applying a high pulse to RST, the microcontroller will reset and all values in registers will be lost.

- Reset values of some 8051 registers

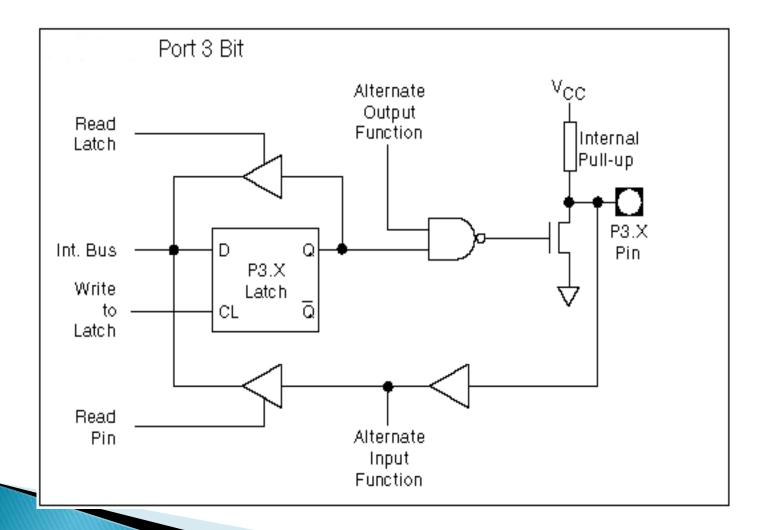

## Port 3 Alternate Functions

| Port Pin | Alternate Function                     |

|----------|----------------------------------------|

| P3.0     | RXD (serial input port)                |

| P3.1     | TXD (serial output port)               |

| P3.2     | INT0 (external interrupt 0)            |

| P3.3     | INT1 (external interrupt 1)            |

| P3.4     | T0 (Timer 0 external input)            |

| P3.5     | T1 (Timer 1 external input)            |

| P3.6     | WR (external data memory write strobe) |

| P3.7     | RD (external data memory read strobe)  |

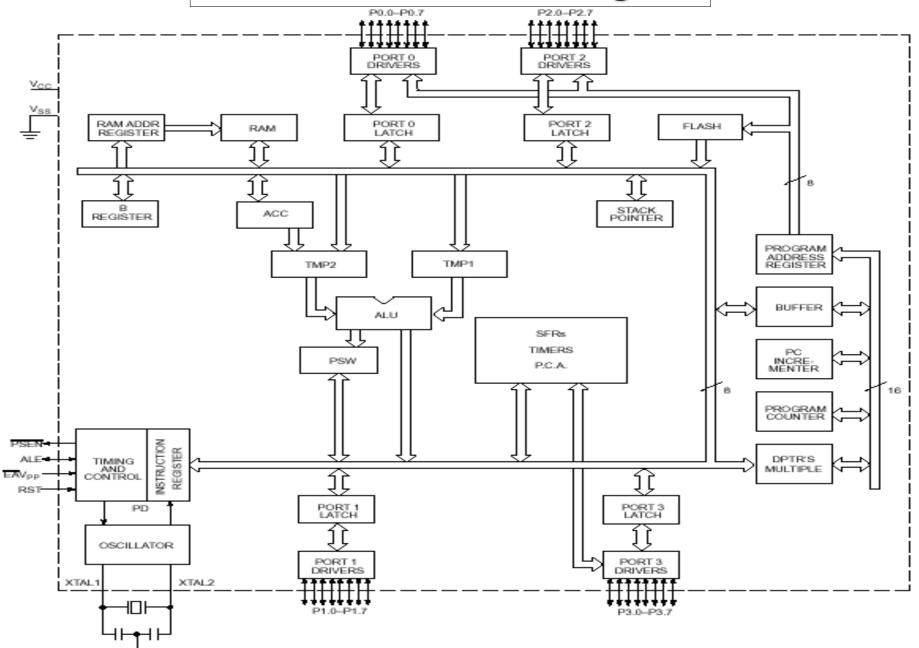

#### **8051 Internal Block Diagram**

## Specific Features OF 8051

- ▶ 8 bit CPU with registers A and B

- 16 bit PC and DPTR(data pointer).

- 8 bit program status word(PSW)

- 8 bit Stack Pointer

- > 32 I/O pins arranged as 4 8 bit ports:P0 to P3

- Two 16 bit timer/counters:T0 and T1

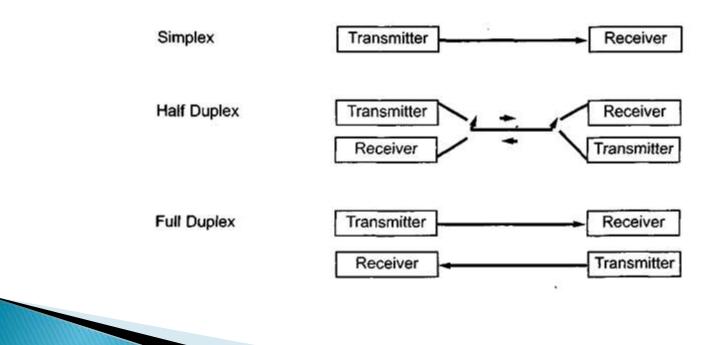

- Full duplex serial data receiver/transmitter

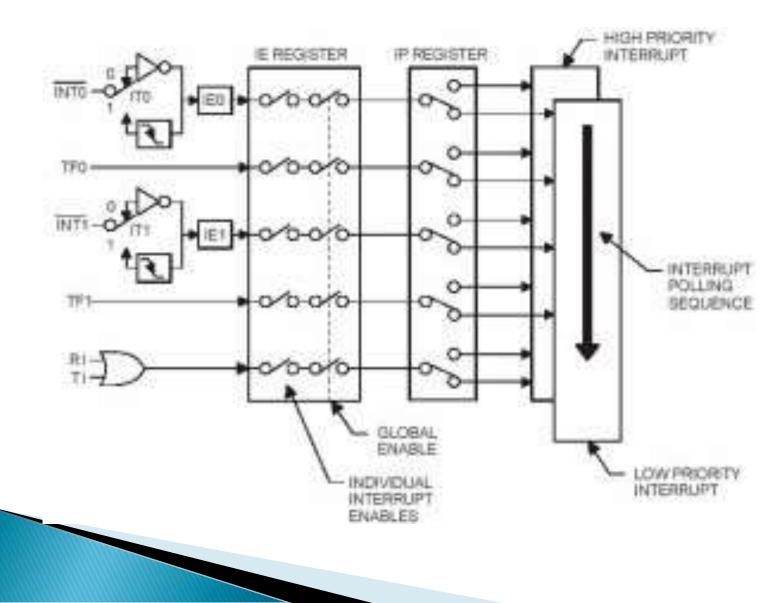

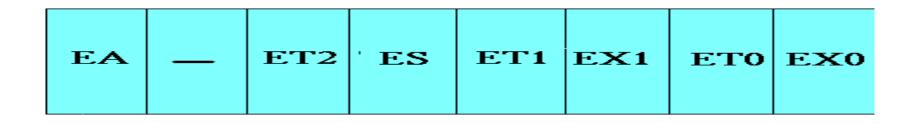

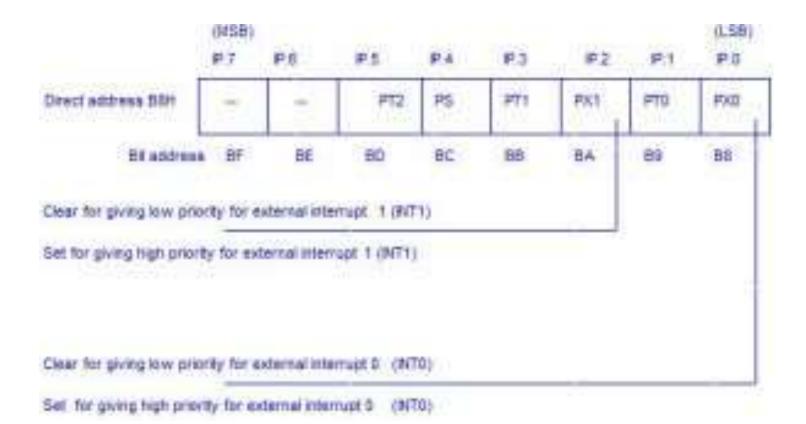

- Control registers : TCON,TMOD,SCON,PCON,IP and IE

- Two external and Three internal interrupt sources.

- Oscillator and Clock Circuits.

- 4K Internal ROM

- 128bytes Internal RAM

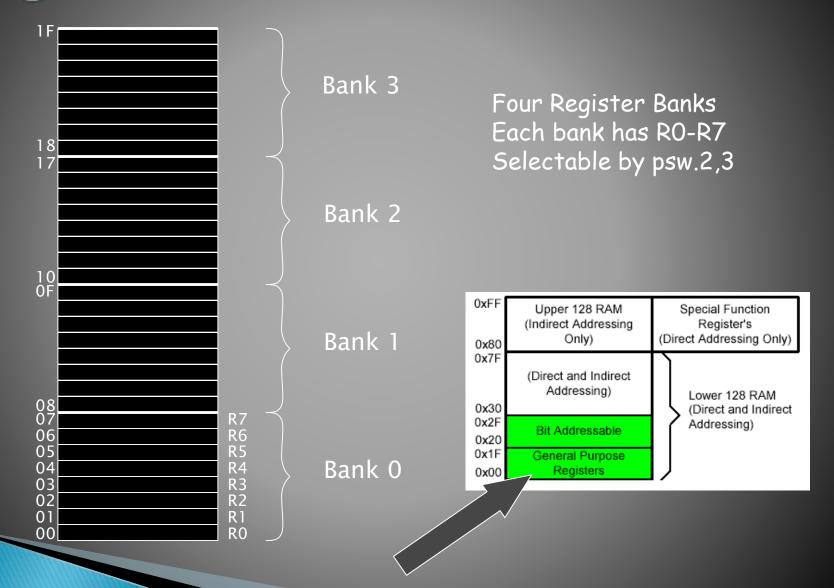

- →4 register banks each having 8 registers

→16 bytes, which may be addressed at the bit level.

→80 bytes of general purpose data memory

Wednesday, November 1, 2023

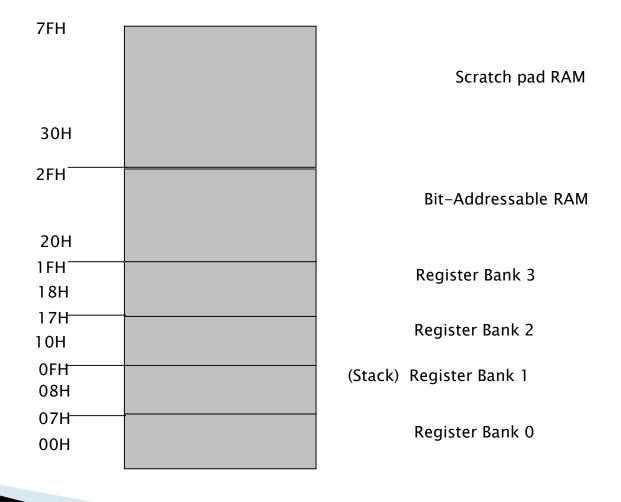

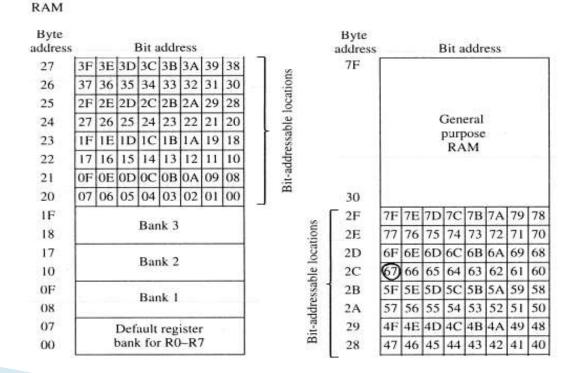

## On-Chip Memory Internal RAM

## **Registers** BanK

# **Register Banks**

- Four banks of 8 byte-sized registers, R0 to R7

- Addresses are :

| 18 – 1F | for bank 3           |

|---------|----------------------|

| 10 – 17 | for bank 2           |

| 08 – 0F | for bank 1           |

| 00 - 07 | for bank 0 (default) |

- Active bank selected by bits [RS1, RS0] in PSW.

- Permits fast "context switching" in interrupt service routines (ISR).

# Registers

|    | _    |

|----|------|

| A  |      |

| В  |      |

| RO | DPTR |

| R1 |      |

| R2 | PC   |

| R3 |      |

| R4 |      |

| R5 |      |

| R6 |      |

| R7 |      |

|    |      |

| DPH | DPL |

|-----|-----|

|     |     |

| Р   | С   |

#### Some 8051 16-bit Register

Some 8-bit **Registers of the** 8051

# The Accumulator

- It is used as a general register to accumulate the results of a large number of instructions.

- It can hold an 8-bit (1-byte) value and is the most versatile register the 8051 has due to the shear number of instructions that make use of the accumulator.

- More than half of the 8051's 255 instructions manipulate or use the accumulator in some way.

## The "R" registers

- The "R" registers are a set of eight registers that are named R0, R1, etc. up to and including R7.

- These registers are used as auxiliary registers in many operations

- > The "R" registers are also used to temporarily store values.

- For example, let's say you want to add the values in R1 and R2 together and then subtract the values of R3 and R4. One way to do this would be:

MOV A,R3 ;Move the value of R3 into the accumulator ADD A,R4 ;Add the value of R4 MOV R5,A ;Store the resulting value temporarily in R5 MOV A,R1 ;Move the value of R1 into the accumulator ADD A,R2 ;Add the value of R2 SUBB A P5 :Subtract the value of P5 (which now contain

**SUBB A,R5** ;Subtract the value of R5 (which now contains R3 + R4)

## The "B" Register

- The "B" register is very similar to the Accumulator in the sense that it may hold an 8-bit (1-byte) value.

- The "B" register is only used by two 8051 instructions: MUL AB and DIV AB. Thus, if you want to quickly and easily multiply or divide A by another number, you may store the other number in "B" and make use of these two instructions.

## The Data Pointer (DPTR)

- The Data Pointer (DPTR) is the 8051's only useraccessable 16-bit (2-byte) register. The Accumulator, "R" registers, and "B" register are all 1-byte values.

- DPTR, as the name suggests, is used to point to data. It is used by a number of commands which allow the 8051 to access external memory.

- DPTR is most often used to point to data in external memory.

## The Program Counter (PC)

- The Program Counter (PC) is a 2-byte address which tells the 8051 where the next instruction to execute is found in memory.

- When the 8051 is initialized PC always starts at 0000h and is incremented each time an instruction is executed.

- It is important to note that PC isn't always incremented by one. Since some instructions require 2 or 3 bytes the PC will be incremented by 2 or 3 in these cases.

## The Stack Pointer (SP)

- The Stack Pointer, like all registers except DPTR and PC, may hold an 8-bit (1-byte) value. The Stack Pointer is used to indicate where the next value to be removed from the stack should be taken from.

- When a value is push onto the stack, the 8051 first increments the value of SP and then stores the value at the resulting memory location.

#### **RESET Value of Some 8051 Registers:**

| Register | Reset Value |

|----------|-------------|

| PC       | 0000        |

| ACC      | 0000        |

| В        | 0000        |

| PSW      | 0000        |

| SP       | 0007        |

| DPTR     | 0000        |

RAM are all zero

### **I/O Ports**

#### Port 0 (pins 32–39)

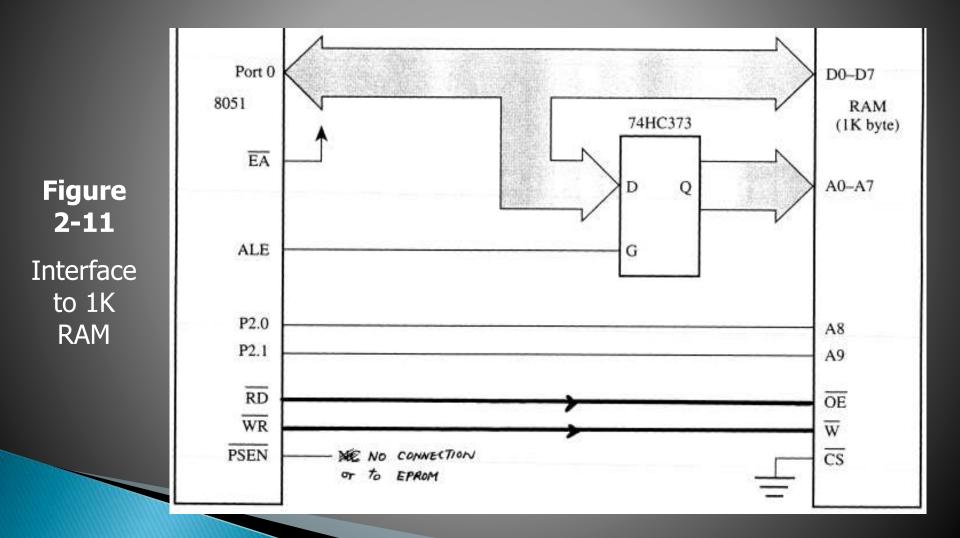

- When connecting an 8051 to an external memory, the 8051 uses ports to send addresses and read instructions.

- 16-bit address : P0 provides both address A0-A7, P2 provides address A8-A15.

- Also, P0 provides data lines D0-D7.

- When P0 is used for address/data multiplexing, it is connected to the 74LS373 to latch the address.

#### Port 1 (pins 1–8)

- Port 1 is denoted by P1.

- P1.0 ~ P1.7

- P1 as an output port (i.e., write CPU data to the external pin)

- P1 as an input port (i.e., read pin data into CPU bus)

Wednesday, November 1, 2023

# **Port 3 ( pins 10-17 )**

- Although port 3 is configured as an output port upon reset, this is not the way it is most commonly used.

- Port 3 has the additional function of providing signals.

- Serial communications signal : RxD, TxD

- External interrupt : /INT0, /INT1

- Timer/counter : T0, T1

- External memory accesses : /WR, /RD

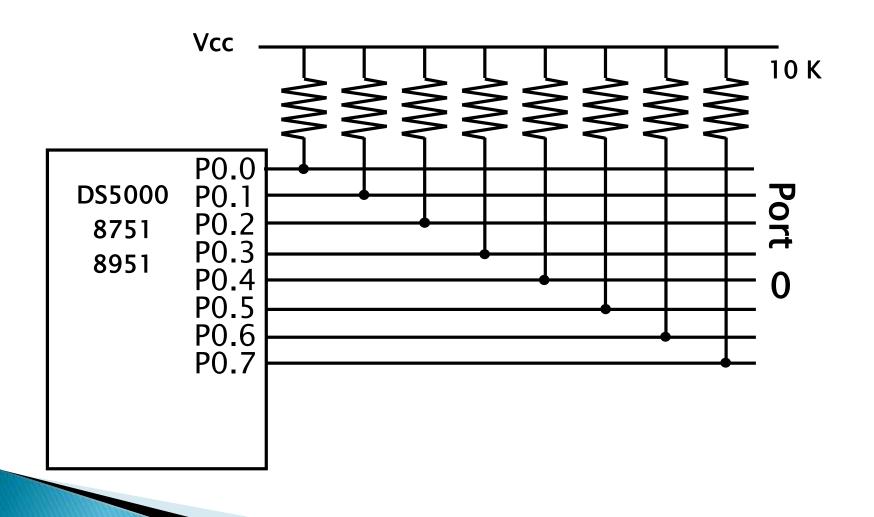

#### **Port 0 with Pull-Up Resistors**

#### 8051 Port 3 Bit Latches and I/O Buffers

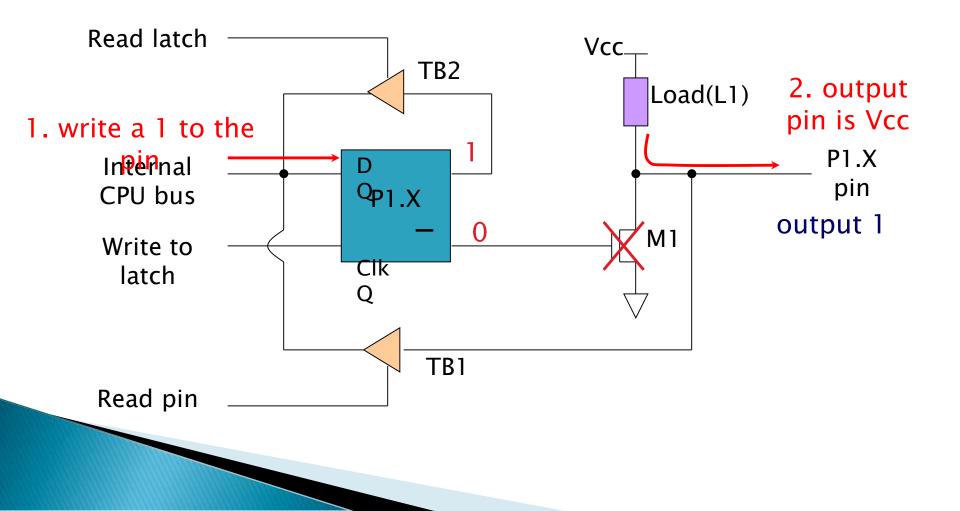

# Writing "1" to Output Pin P1.X

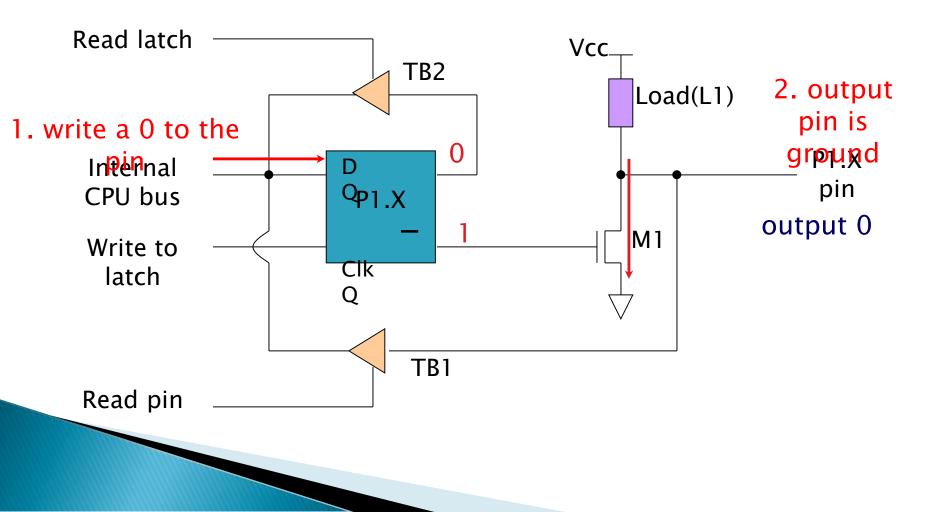

# Writing "O" to Output Pin P1.X

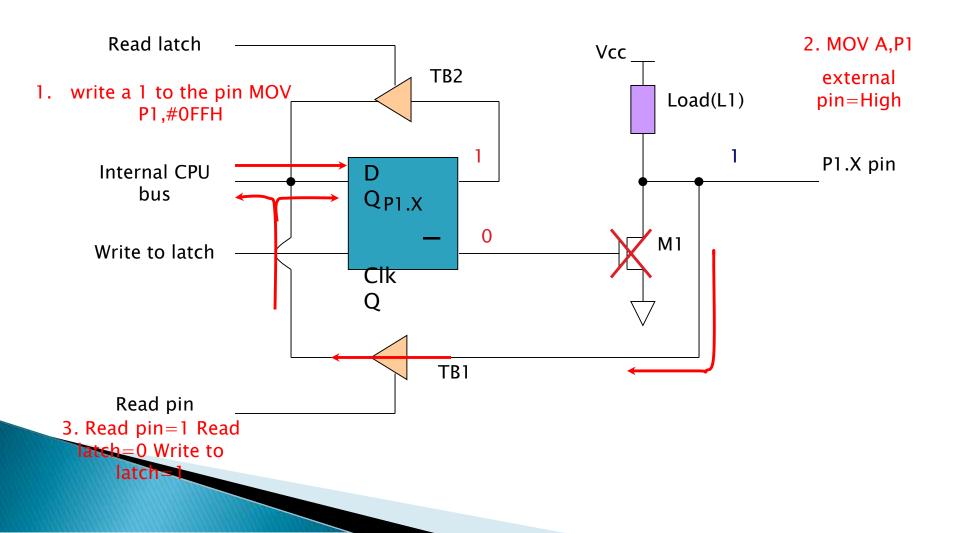

# Reading "High" at Input Pin

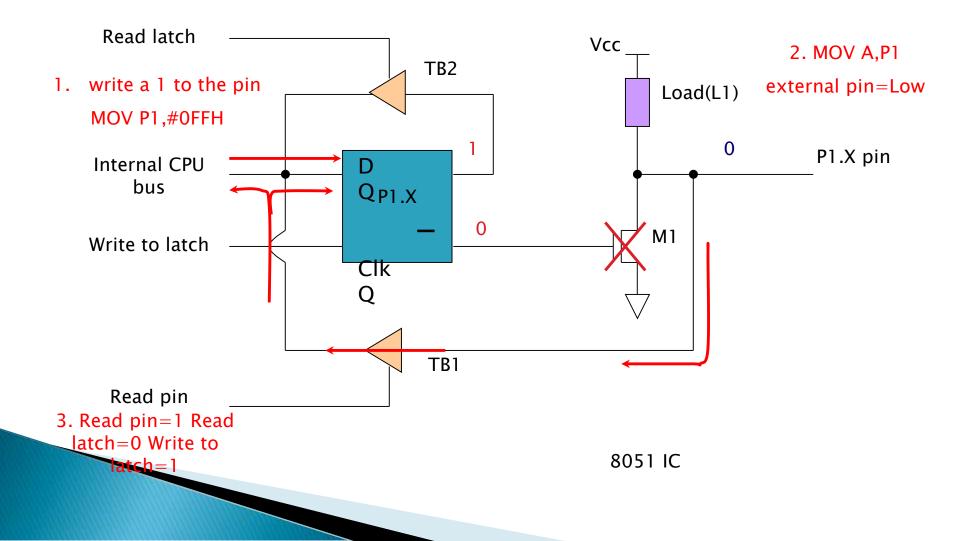

# Reading "Low" at Input Pin

## Port 0 with Pull-Up Resistors

## 8051 Memory Organization

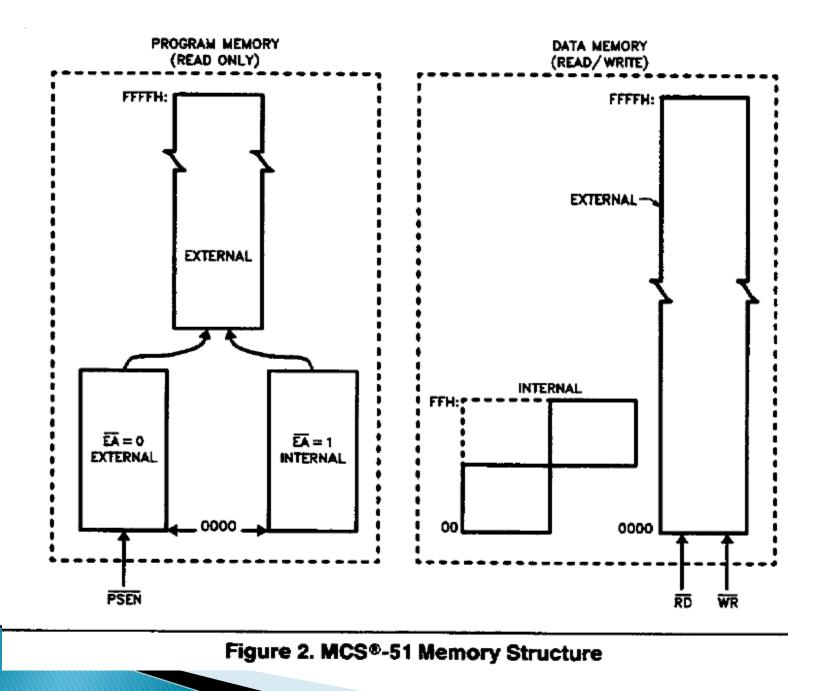

- The 8051 microcontroller's memory is divided into Program Memory and Data Memory.

- Program Memory (ROM) is used for permanent saving program being executed,

- Data Memory (RAM) is used for temporarily storing and keeping intermediate results and variables.

### Program Memory (ROM)/Code Memory

- Program Memory (ROM) is used for permanent saving program (CODE) being executed. The memory is read only.

- Depending on the settings made in compiler, program memory may also used to store a constant variables. The 8051 executes programs stored in program memory only.

- Code memory type specifier is used to refer to program memory.

- 8051 memory organization allows external program memory to be added.

- How does the microcontroller handle external memory depends on the pin EA logical state.

# **Program Memory**

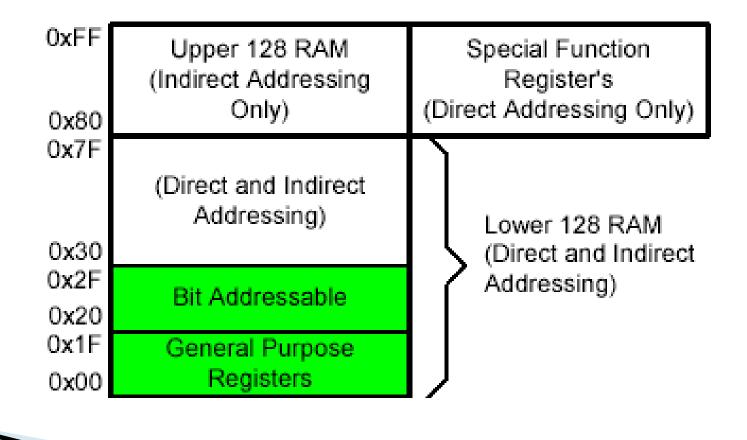

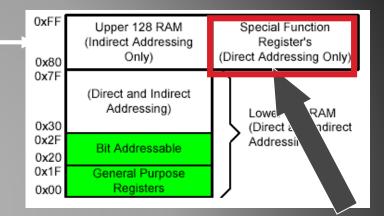

## Internal Data Memory

- Up to 256 bytes of internal data memory is available

- Locations available to the user occupy addressing space from 0 to 7Fh, i.e. first 128 registers and this part of RAM is divided in several blocks.

- The first 128 bytes of internal data memory are both directly and indirectly addressable.

- The upper 128 bytes of data memory (from 0x80 to 0xFF) can be addressed only indirectly.

# **Memory Organization**

RAM memory space allocation in the 8051

Wednesday, November 1, 2023

# **Bit Addressable Memory**

- Memory block in the range of 20h to 2Fh is bit-addressable, which means that each bit being there has its own address from 0 to 7Fh.

- Since there are 16 such registers, this block contains in total of 128 bits with separate addresses (Bit 0 of byte 20h has the bit address 0, and bit 7 of byte 2Fh has the bit address 7Fh).

### **External Data Memory**

- Access to external memory is slower than access to internal data memory.

- There may be up to 64K Bytes of external data memory.

- Several 8051 devices provide on-chip XRAM space that is accessed with the same instructions as the traditional external data space.

- This XRAM space is typically enabled via proper setting of SFR register and overlaps the external memory space.

- Setting of that register must be manually done in code, before any access to external memory or XRAM space is made.

#### Address Multiplexing for External Program/Code Memory

D0-D7 Port 0 EPROM 8051 74HC373 Figure 2-8 ĒA Q A0-A7 D Accessing external ALE G code memory A8-A15 Port 2 PSEN OE

### Accessing External Data Memory

# **Special Function Registers**

- SFRs which are also bit addressable

A, B, IP, IE, TCON, SCON, PSW, P0, P1, P2, P3

- Other SFRs TMOD, THO, TLO, TH1, TL1, SBUF, PCON, SP, DPTR

# **Special Function Registers**

#### DATA registers

#### **CONTROL** registers

- Timers

- Serial ports

- Interrupt system

- Analog to Digital converter

- Digital to Analog converter

Etc.

Addresses 80h - FFh

Direct Addressing used to access SPRs

**Special Function Registers**

| Name | Function                 | Name | Function                    |

|------|--------------------------|------|-----------------------------|

| A    | Accumulator              | SBUF | Serial Port data<br>buffer  |

| В    | Arithmetic               | SP   | Stack Pointer               |

| DPH  | Addressing Ext<br>Memory | TMOD | Timer/Counter<br>mode cntrl |

| DPL  | Addressing Ext<br>Memory | TCON | Timer/Counter<br>cntrl      |

| IE   | Interrupt enable         | TL0  | Timer0 lower byte           |

| IP   | Interrupt Priority       | TH0  | Timer0 higher<br>byte       |

| P0   | I/O Port Latch           | TL1  | Timer1 lower byte           |

| P1   | I/O Port Latch           | TH1  | Timer1 higher<br>byte       |

| P2   | I/O Port Latch           |      |                             |

| Р3   | I/O Port Latch           |      |                             |

| PCON | Power Control            |      |                             |

| PSW  | Pam Status               |      |                             |

#### SFR MEMORY MAP

8 Bytes

|           |       |      |        | _        |     |     |      | _    |

|-----------|-------|------|--------|----------|-----|-----|------|------|

| F8        |       |      |        |          |     |     |      | FF   |

| F0        | В     |      |        |          |     |     |      | F7   |

| E8        |       |      |        |          |     |     |      | EF   |

| E0        | ACC   |      |        |          |     |     |      | E7   |

| D8        |       |      |        |          |     |     |      | DF   |

| D0        | PSW   |      |        |          |     |     |      | D7   |

| C8        | T2CON |      | RCAP2L | RCAP2H   | TL2 | TH2 |      | CF   |

| C0        |       |      |        |          |     |     |      | _ C7 |

| B8        | IP    |      |        |          |     |     |      | BF   |

| B0        | P3    |      |        |          |     |     |      | B7   |

| <b>A8</b> | IE    |      |        |          |     |     |      | AF   |

| AO        | P2    |      |        |          |     |     |      | A7   |

| 98        | SCON  | SBUF |        |          |     |     |      | 9F   |

| 90        | P1    |      |        |          |     |     |      | 97   |

| 88        | TCON  | TMOD | TL0    | TL1      | THO | TH1 |      | 8F   |

| 80        | P0    | SP   | DPL    | DPH      |     |     | PCON | 87   |

|           | ↑     |      |        | Figure 5 |     |     |      | _    |

Figure 5

Bit

Addressable

#### **PSW: PROGRAM STATUS WORD. BIT ADDRESSABLE.**

| CY          | AC            | F0         | RS1                       | RS0                       | ov          | _                                       | P        |

|-------------|---------------|------------|---------------------------|---------------------------|-------------|-----------------------------------------|----------|

| CY          | PSW.7         | Carry Fla  |                           | •                         |             | • · · · · · · · · · · · · · · · · · · · | <u> </u> |

| AC          | PSW.6         | Auxiliary  | Carry Flag                |                           |             |                                         |          |

| <b>F</b> 0  | PSW.5         | Flag 0 av  | ailable to th             | ne user for g             | eneral pur  | oose.                                   |          |

| RS1         | PSW.4         | Register 1 | Bank selecte              | or bit 1 (SEI             | E NOTE 1)   | ).                                      |          |

| <b>RS</b> 0 | <b>PSW.3</b>  | Register 1 | Bank selecte              | or bit 0 (SEI             | E NOTE 1)   | ).                                      |          |

| ov          | PSW.2         | Overflow   | Flag.                     |                           |             |                                         |          |

| _           | <b>PSW.1</b>  | User defin | nable flag.               |                           |             |                                         |          |

| Р           | <b>PSW</b> .0 |            | g. Set/clear<br>the accum | ed by hardward<br>ulator. | are each in | struction (                             | cycle to |

#### NOTE:

1. The value presented by RS0 and RS1 selects the corresponding register bank.

| RS1 | RS0 | Register Bank | Address |

|-----|-----|---------------|---------|

| 0   | 0   | 0             | 00H-07H |

| 0   | 1   | 1             | 08H-0FH |

| 1   | 0   | 2             | 10H-17H |

| 1   | 1   | 3             | 18H-1FH |

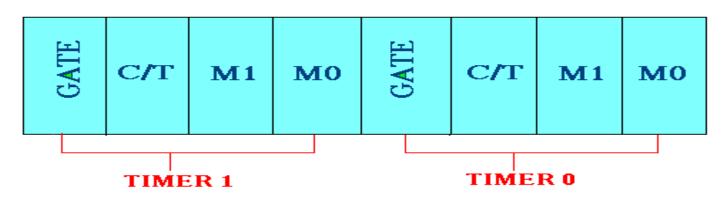

#### **TMOD Register:**

•Gate: When set, timer only runs while INT(0,1) is high.

C/T : Counter/Timer select bit.

|                   | IVII | INIO | WODE                                   |

|-------------------|------|------|----------------------------------------|

| •M1 : Mode bit 1. | 0    | 0    | 13-bit timer mode<br>16-bit timer mode |

|                   | 0    | 1    | 16-bit timer mode                      |

| MO: Mode bit 0.   | 1    | 0    | 8-bit auto-reload mode<br>split mode   |

|                   | 1    | 1    | split mode                             |

|                   |      |      | 1                                      |

M1 . M0 IMODE

#### **TCON Register:**

| TF1 TR1 TF0 TF | O IE1 IT1 | IEO ITO |

|----------------|-----------|---------|

|----------------|-----------|---------|

- •TF1: Timer 1 overflow flag.

- TR1: Timer 1 run control bit.

- •TF0: Timer 0 overflag.

- TR0: Timer 0 run control bit.

- IE1: External interrupt 1 edge flag.

- IT1: External interrupt 1 type flag.

- •IE0: External interrupt 0 edge flag.

- ITO: External interrupt 0 type flag.

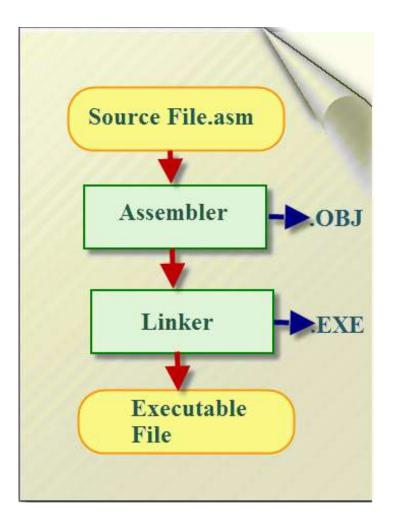

# CHAPTER 7

#### Instruction Set and Addressing Modes of 8051

The way in which the instruction is specified.

- ←Immediate

- ◆Register

- ◆Direct

- Register IndirectIndexed

### **Immediate Addressing Mode**

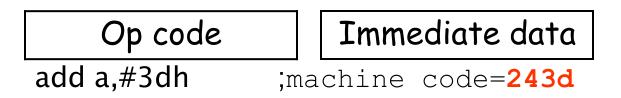

Immediate Data is specified in the instruction itself

◆Egs:

MOV A,#65H

MOV A,#'A'

MOV R6,#65H

MOV DPTR,#2343H

MOV P1,#65H

Sunday, August 23, 2020

### **Register Addressing Mode**

MOV Rn, A ;n=0,...,7 ADD A, Rn MOV DPL, R6

MOV DPTR, A MOV Rm Rp

Sunday, August 23, 2020

### **Direct Addressing Mode**

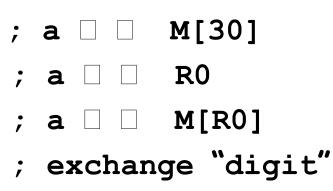

Although the entire of 128 bytes of RAM can be accessed using direct addressing mode, it is most often used to access RAM loc. 30 - 7FH.

MOV R0, 40H MOV 56H, A MOV A, 4 MOV 6, 2

- ;  $\equiv$  MOV A, R4

- ; copy R2 to R6

- ; MOV R6,R2 is invalid !

### **Register Indirect Addressing Mode**

← In this mode, register is used as a pointer to the data.

MOV A,@Ri

; move content of RAM loc. Where address is held by Ri into A (i=0 or 1)

#### MOV @R1,B

In other word, the content of register R0 or R1 is sources or target in MOV, ADD and SUBB instructions.

⊠>\_jump

#### Indexed Addressing Mode And On-Chip ROM Access

This mode is widely used in accessing data elements of look-up table entries located in the program (code) space ROM at the 8051

### MOVC A,@A+DPTRA= content of address A +DPTR from ROM

#### Note:

Because the data elements are stored in the program (code ) space ROM of the 8051, it uses the instruction MOVC instead of MOV. The "C" means code.

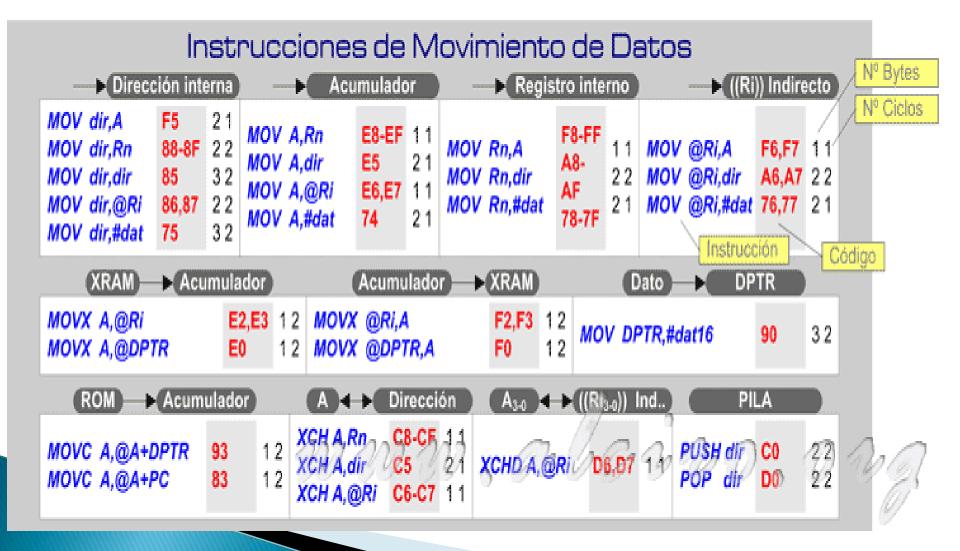

### The 8051 Assembly Language

- Data transfer instructions

- Addressing modes

- Data processing (arithmetic and logic)

- Program flow instructions

### **Data Transfer Instructions**

### ◆MOV dest, source dest □ source

#### Stack instructions

- PUSH byte; increment stack pointer,<br/>; move byte on stackPOP byte; move from stack to byte,

- ;decrement stack pointer

#### Exchange instructions

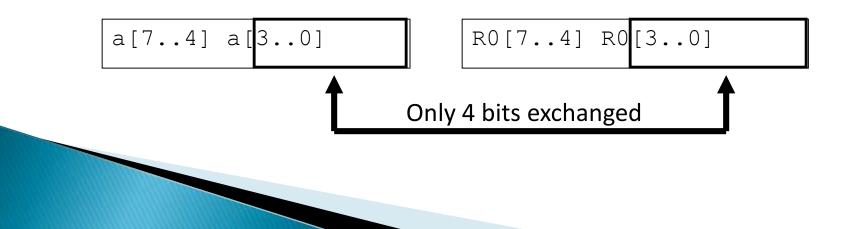

XCH a, byte ;exchange accumulator and byte

XCHD a, byte ;exchange low nibbles of

;accumulator and byte

#### <u>Immediate Mode</u> – specify data by its value

- **mov A, #0** ;put 0 in the accumulator ;A = 00000000

- mov R4, #11h ;put 11hex in the R4 register

;R4 = 00010001

- mov B, #11 ;put 11 decimal in b register

;B = 00001011

- mov DPTR,#7521h ;put 7521 hex in DPTR

;DPTR = 0111010100100001

#### Immediate Mode - continue

#### MOV DPTR, #7521h

MOV DPL,#21H MOV DPH, #75

COUNT EGU 30 ~ mov R4, #COUNT

MOV DPTR, #MYDATA ~ ORG 200H MYDATA:DB "IRAN"

# <u>Register Addressing</u> – either source or destination is one of CPU register

- MOV R0,A

- MOV A, R7

- ADD A,R4

- ADD A,R7

- MOV DPTR, #25F5H

- MOV R5, DPL

- MOV R, DPH

#### Note that MOV R4, R7 is incorrect

#### Direct Mode – specify data by its 8-bit address Usually for 30h-7Fh of RAM

| Mov | a,   | 70h  |

|-----|------|------|

| Mov | R0 / | ,40h |

| Mov | 561  | ı,a  |

| Mov | 0D0  | )h,a |

- ; copy contents of RAM at 70h to a

- ; copy contents of RAM at 70h to a

- ; put contents of a at 56h to a

- ; put contents of a into PSW

#### DATA MEMORY (RAM)

#### INTERNAL DATA ADDRESS SPACE

| 0×FF<br>0×80 | Upper 128 RAM<br>(Indirect Addressing<br>Only) | Special Function<br>Register's<br>(Direct Addressing Only) |

|--------------|------------------------------------------------|------------------------------------------------------------|

| 0x7F<br>0x30 | (Direct and Indirect<br>Addressing)            | Lower 128 RAM<br>(Direct and Indirect                      |

| 0x2F<br>0x20 | Bit Addressable                                | Addressing)                                                |

| 0x1F<br>0x00 | General Purpose<br>Registers                   |                                                            |

**Direct Mode** – play with R0–R7 by direct address

- $MOV A, 4 \equiv MOV A, R4$

- $MOV A, 7 \equiv MOV A, R7$

- MOV 7,2  $\equiv$  MOV 87,R6

- MOV R2,#5 ;Put 5 in R2

- MOV R2,5 ;Put content of RAM at 5 in R2

<u>Register Indirect</u> – the address of the source or destination is specified in registers

Uses registers R0 or R1 for 8-bit address:

mov psw, #0 ; use register bank 0

mov r0, #0x3C

mov @r0, #3 ; memory at 3C gets #3

; M[3C] 3

Uses DPTR register for 16-bit addresses:

mov dptr, #0x9000 ; dptr 9000h

movx a, @dptr ; a M[9000]

Note that 9000 is an address in external memory

<u>Register Indexed Mode</u> – source or destination address is the sum of the <u>base address</u> and the accumulator(Index)

Base address can be DPTR or PC mov dptr, #4000h mov a, #5 movc a, @a + dptr ;a M[4005]

Acc Register

- A register can be accessed by direct and register mode

- This 3 instruction has same function with different code

| 0703 | E500   | mov | a,00h    |

|------|--------|-----|----------|

| 0705 | 8500E0 | mov | acc,00h  |

| 0708 | 8500E0 | mov | 0e0h,00h |

◆ Also this 3 instruction

070B E9

070C 89E0

070E 89E0

mov a,r1

mov acc,r1

mov 0e0h,r1

### SFRs Address

← B – always direct mode – except in MUL & DIV

| 0703 8 | 500 <mark>F0</mark> | mov | <mark>b</mark> ,00h     |

|--------|---------------------|-----|-------------------------|

| 0706 8 | 500F0               | mov | 0 <mark>f0</mark> h,00h |

| 0709 8 | CF0                 | mov | b,r4                    |

| 070B 8 | CF0                 | mov | 0f0h,r4                 |

P0~P3 – are direct address

0704 F580 mov p0,a

0706 F580 mov 80h,a

0708 859080 mov p0,p1

← Also other SFRs (pcon, tmod, psw,....)

### **8051 Instruction Format**

#### fimmediate addressing

#### Direct addressing

### Stack

Stack-oriented data transfer

- Only one operand (direct addressing)

- SP is other operand register indirect implied

- Direct addressing mode must be used in Push and Pop

| mov sp, $#0x40$ | ; Initialize SP            |

|-----------------|----------------------------|

| push 0x55       | ; SP 🗌 SP+1, M[SP] 🗌 M[55] |

|                 | ; M[41] 🗌 M[55]            |

| pop b           | ; b 🗌 M[55]                |

Note: can only specify RAM or SFRs (direct mode) to push or pop. Therefore, to push/pop the accumulator, must use acc, not a

Stack (push, pop)

#### ← Therefore

| Push | a    | ;is | invalid |  |

|------|------|-----|---------|--|

| Push | r0   | ;is | invalid |  |

| Push | r1   | ;is | invalid |  |

| push | acc  | ;is | correct |  |

| Push | psw  | ;is | correct |  |

| Push | b    | ;is | correct |  |

| Push | 13h  |     |         |  |

| Push | 0    |     |         |  |

| Push | 1    |     |         |  |

| Pop  | 7    |     |         |  |

| Pop  | 8    |     |         |  |

| Push | 0e0h | ;ac | cc      |  |

| Pop  | 0f0h | ;b  |         |  |

|      |      |     |         |  |

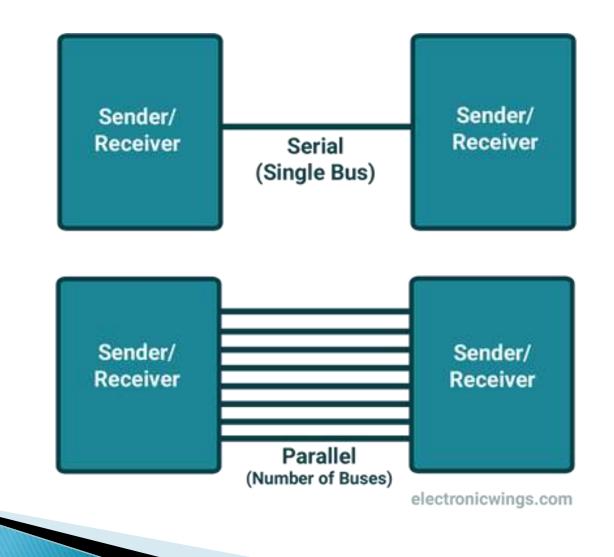

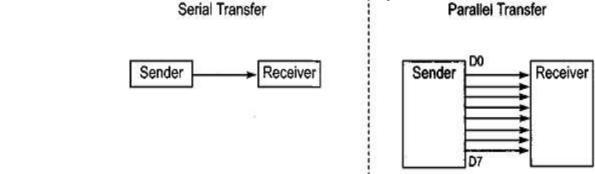

# Serial Port operation

- Serial communication means transfer data bit by bit serially at a time, where as in parallel communication, the number of bits that can be transferred at a time depends upon the number of data lines available for communication.

- Two methods of serial communication are

- Synchronous Communication: Transfer of bulk data in framed structure at a time

- Asynchronous Communication: Transfer of a byte data in framed structure at a time

- ◆ 8051 has built in UART with RXD (serial data receive pin) and TXD (serial data transmit pin) on PORT3.0 and PORT3.1 respectively.

### **Communication Mode**

### Asynchronous communication

- Asynchronous serial communication is widely used for byte oriented transmission.

- ← Frame structure in Asynchronous communication:

- START bit: It is a bit with which serial communication start and it is always low.

- Data bits packet: Data bits can be 5 to 9 bits packet. Normally we use 8 data bit packet, which is always sent after START bit.

- STOP bit: This is one or two bits. It is sent after data bits packet to indicate end of frame. Stop bit is always logic high.

- In asynchronous serial communication frame, first START bit followed by data byte and at last STOP bit, forms a 10-bit frame. Sometimes last bit is also used as parity bit.

#### Data transmission rate

- Data transmission rate is measured in bits per second (bps). In binary system it is also called as baud rate (number of signal changes per second).

- Standard baud rates supported are 1200, 2400, 4800, 19200, 38400, 57600, and 115200. Normally most of the time 9600 bps is used when speed is not a big issue.

### Serial communication Registers

#### SBUF: Serial Buffer Register

This is the serial communication data register used to transmit or receive data through it.

#### **SCON:** Serial Control Register

Serial control register SCON is used to set serial communication operation modes. Also it is used to control transmit and receive operations.

# SCON

| 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |      |

|-----|-----|-----|-----|-----|-----|----|----|------|

| SM0 | SM1 | SM2 | REN | TB8 | RB8 | TI | RI | SCON |

| Mode | SM0 | SM1 | Mode                                                      |

|------|-----|-----|-----------------------------------------------------------|

| 0    | 0   | 0   | 1/12 of Osc frequency shift register mode fixed baud rate |

| 1    | 0   | 1   | 8-bit UART with timer 1 determined baud rate              |

| 2    | 1   | 0   | 9-bit UART with 1/32 of Osc fixed baud rate               |

| 3    | 1   | 1   | 9-bit UART with timer 1 determined baud rate              |

Bit 7:6 - SM0:SM1: Serial Mode Specifier

Normally mode-1 (SM0 =0, SM1=1) is used with 8 data bits, 1 start bit and 1 stop bit.

# SCON

- ← Bit 5 SM2: for Multiprocessor Communication

- This bit enables multiprocessor communication feature in mode 2 & 3.

- ← Bit 4 REN: Receive Enable

- 1 = Receive enable

- 0 = Receive disable

- Bit 3 TB8: 9th Transmit Bit

- This is 9th bit which is to be transmitted in mode 2 & 3 (9-bit mode)

- ← Bit 2 RB8: 9th Receive Bit

- This is 9th received bit in mode 2 & 3 (9-bit mode), where as in mode 1, if SM2 = 0 then RB8 hold stop bit that received

- Bit 1 TI: Transmit Interrupt Flag

- This bit indicates transmission is complete and gets set after transmitting the byte from buffer. Normally TI (Transmit Interrupt Flag) is set by hardware at the end of 8th bit in mode 0 and at the beginning of stop bit in other modes.

- ← Bit 0 RI: Receive Interrupt Flag

- This bit indicates reception is complete and gets set after receiving the complete byte in buffer. Normally RI (Receive Interrupt Flag) is set by hardware in receiving mode at the end of 8th bit in mode 0 and at the stop bit receive time in other modes.

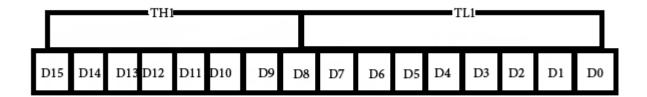

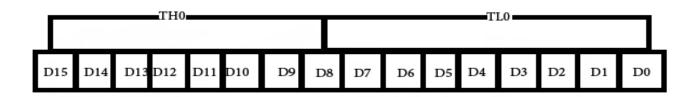

### **Timer Operations**

- The 8051 has two counters/timers which can be used either as timer to generate a time delay or as counter to count events happening outside the microcontroller.

- he 8051 has two timers: timer0 and timer1. They can be used either as timers or as counters. Both timers are 16 bits wide. Since the 8051 has an 8-bit architecture, each 16bit is accessed as two separate registers of low byte and high byte.

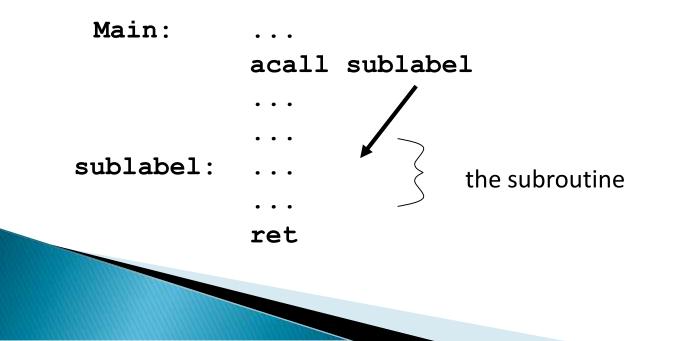

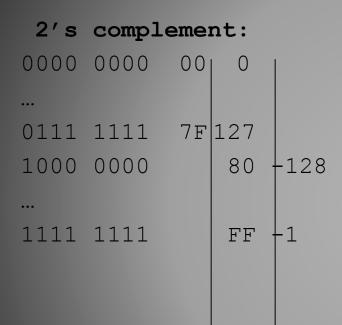

# **Timer0 registers**